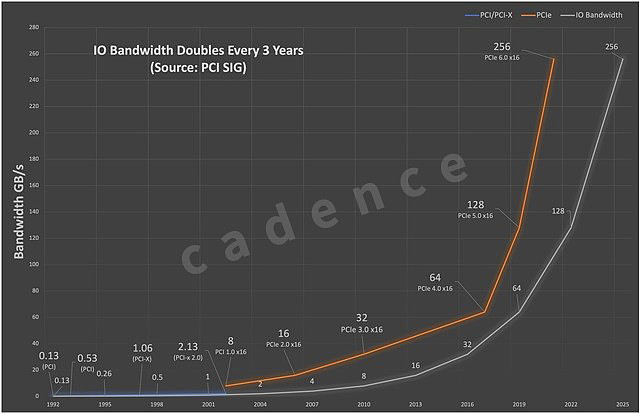

在今年3月,Rambus对外发布了PCIe 6.0控制器,在这个活动中,Rambus战略营销副总裁 Matt Jones、Rambus大中华区总经理苏雷将PCIe从1.0~PCIe 6.0,每一次技术升级带来的是传输带宽翻番的趋势,以及PCIe 6.0控制器实现带宽翻番的一些技术细节讲清楚了,如需要将信号调制由NRZ(PAM2)升级为PAM4,从2电压等级提升到4,响应的传输数位由1提升到2。

同时Matt Jones指出:PAM4需要配套更强的前向纠错(FEC)算法,需要配套采用固定大小数据包(FLIT)等限制,PCIe 6.0控制器支持动态信道分配,因此具有更好的节能的效果(内容详见“Rambus铺就“通往PCIe 6.0的天梯”一文)。

但相比技术,相信更加用户会关注应用的问题。

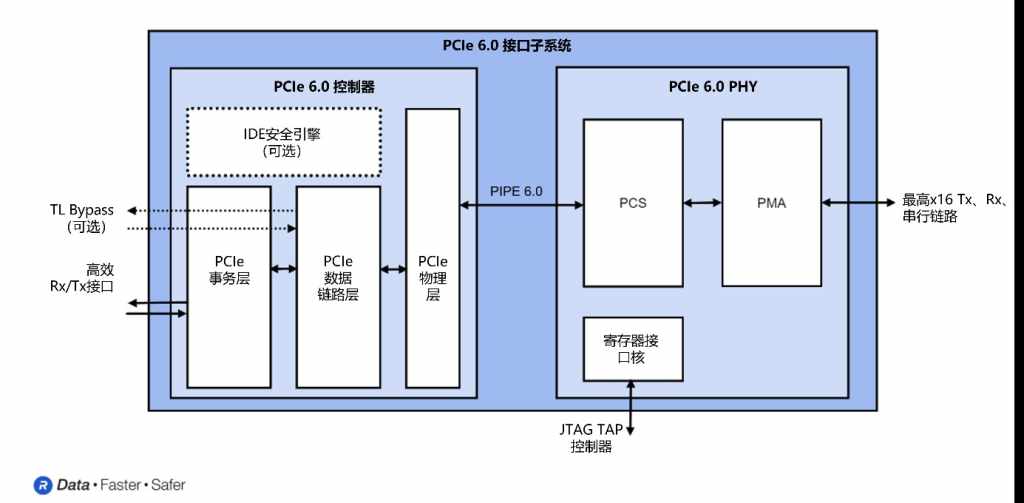

12月1日,Rambus宣布推出PCIe 6.0接口子系统。这一次, Matt Jones把应用问题讲清楚了。

作为CXL 3.0软件栈协议规范的物理连接承载平台,PCIe 6.0主要用于CPU与GPU(AI加速器)、CPU与DPU(智能万卡NIC)、以及CXL内存模块(可以理解为其他CPU DDR内存)的连接,对应的应用场景,如大内存、以及不同外设缓存之间的直接数据交换。

对于这些场景而言,PCIe 6.0接口子系统高达64GT/s的数据传输速率,对于异构计算架构的影响意义重大。

Ranmbus此次发布的PCIe 6.0接口子系统,其控制器在实现性能、速度的同时,也提供了完整性和可靠性质量保障,与此同时,附件提供的数据加密(IDE)引擎,为保障数据安全传输提供了新的选择,丰富安全报站。专门用于保护PCIe链接和通过它们传输的重要数据,PCIe 6.0接口子系统保持了原有PHY(Port Physical Layer,端口物理层),有利于系统兼容性,复用主板设计现有的很多技术规范和经验积累。

Rambus PCIe 6.0接口子系统有以下主要特性:

- 支持PCIe 6.0规范,包括64 GT/s数据传输速率和PAM4调制信号

- 实现低延迟前向纠错(FEC),保证链路稳健性

- 支持固定尺寸的FLIT,可实现高带宽效率

- 向后兼容PCIe 5.0、4.0和3.0/3.1

- 通过IDE引擎(控制器)实现最先进的安全性

- 支持CXL 3.0,用于优化内存资源的新使用模式(PHY)

都是“吃一个、挟一个、看一个”,PCIe 6.0显然就是需要“挟一个”的技术,预计到2025年,其市场会趋于成熟,未雨绸缪,服务器厂商需要提前布局。

时间转瞬即逝,很快的!