2012年4月11日、12日,IDF(英特尔信息技术峰会)在北京国家饭店隆重举行。本届IDF以“引领潮流,直面未来”为主题。Ivy Bridge架构作为英特尔22nm制程工艺的第一款产品,是本次大会的一个重点。

在下午的技术课程中,来自英特尔的功耗控制单元专家Varghese George介绍了Ivy Bridge处理器内核中的创新,英特尔中国研究院的专家江红博士介绍了Ivy Bridge核芯显卡的创新。本文对技术课程的内容做了概述。【更多关于IDF的精彩报道请关注:DOIT直播专题】

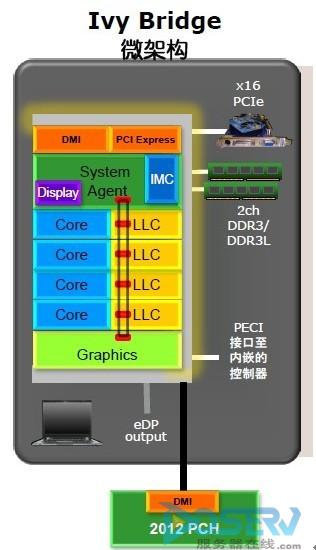

和前一代架构相比,Ivy Bridge虽然依然是CPU+GPU双芯片的布局,但是在工艺制程、图形/媒体处理器、IA核心/指令集架构(ISA)、安全、能耗管理和内存实现方面都有许多技术创新。

22nm制程工艺

Ivy Bridge是属于Tick的范畴,从上一代的32nm的制程工艺,全面切换到了具有更高的性能和更低的功能的22nm制程工艺。22nm究竟多大?就像马宏升在上午的主题演讲中所说的,22nm是用肉眼看不到的,一亿个这么大的晶体管能够装到一个枕头上,用马宏升的话说,这是一个“科学奇迹”。

图形/媒体处理器

新一代的微架构能带来更高的3D性能,并且支持Microsoft DirectX 11,在媒体处理器功能和性能提升显著。

IA核心/指令集架构(ISA)的显著改变

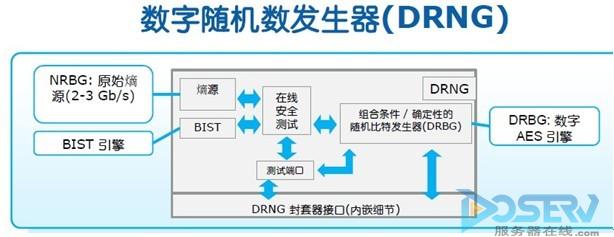

数字随机数发生器(DRNG):Ivy Bridge引用了一个高质量/高性能的数字随机数发生器DRNG。(如下图所示)这个DRNG是为了符合各类标准而设计的,如ANSIx9.82、NIST SP 800-90以及NIST FIPS 140-2/3 Level 2等。通过“RDRAND-可供所有特权级/运行模式使用”指令,可以把一个随机数(可以是16位、32位或者是64位)返回到目的寄存器,RDRAND通过CPUID.1.ECX[30]引用。

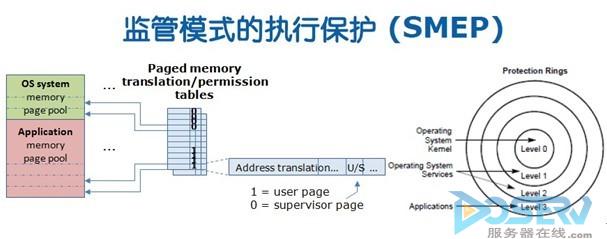

监管模式的执行保护(SMEP):Ivy Bridge引入了SMEP来帮助防止EoP(越权)安全攻击,比如说在较高级特权级运行时溢出到不可信的应用内存区域执行。如果CR4.SMEP设定为1而且是在监管模式(CPL<3),那么来自用户模式为1的线性地址的指令不会被执行。SMEP在32位和64位的运行模式下都可使用,使用的方式为通过CPUID.7.0EBX[7]引用。

能耗管理

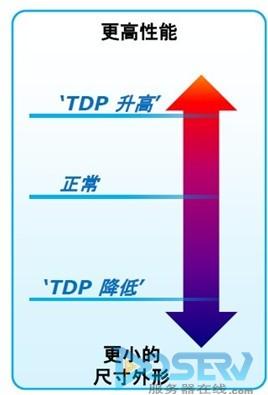

可配置的TDP和低功耗模式:可配置的TDP允许在一个CPU上实现多个不同的TPD能耗水平,因为动态变化的能耗/性能范围更大(如下图所示),并且基于运行中的触发器动态变迁;低功耗模式定义了CPU的最低能耗,英特尔提供了驱动程序实现上述2种功能,可配置的TDP和低功耗模式允许OEM更加灵活地设计更具有弹性的系统。

在典型的工作负载中,Ivy Bridge芯片的平均功耗最高可以改善20%。

PCI-e 3.0:IVB芯片上支持3个第三代控制器和16条数据线,16条数据线的组合形式可以为1×16、2×8或者是1×8+2×4。并且支持PCIe ASPM所有的能耗状态,包括L0s、L1。向后兼容PCI-E第一代和第二代的板卡。

Ivy Bridge核心显卡

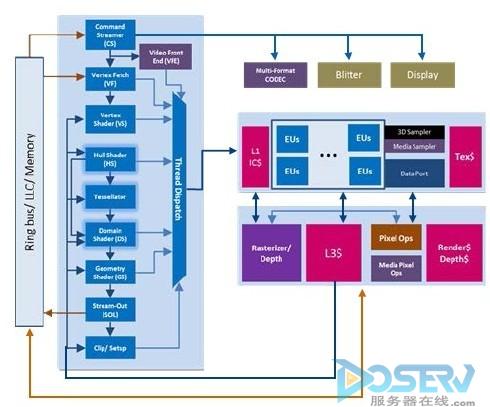

图 Ivy Bridge核心显卡架构

由上图可看出,Ivy Bridge新的“弹性”架构分为5个区域:全局单元、模块阵列共享区、模块阵列区、视频CODEC和显示单元。Ivy Bridge核心显卡在3D微架构、可编程性和能耗方面都有了很大的改善。