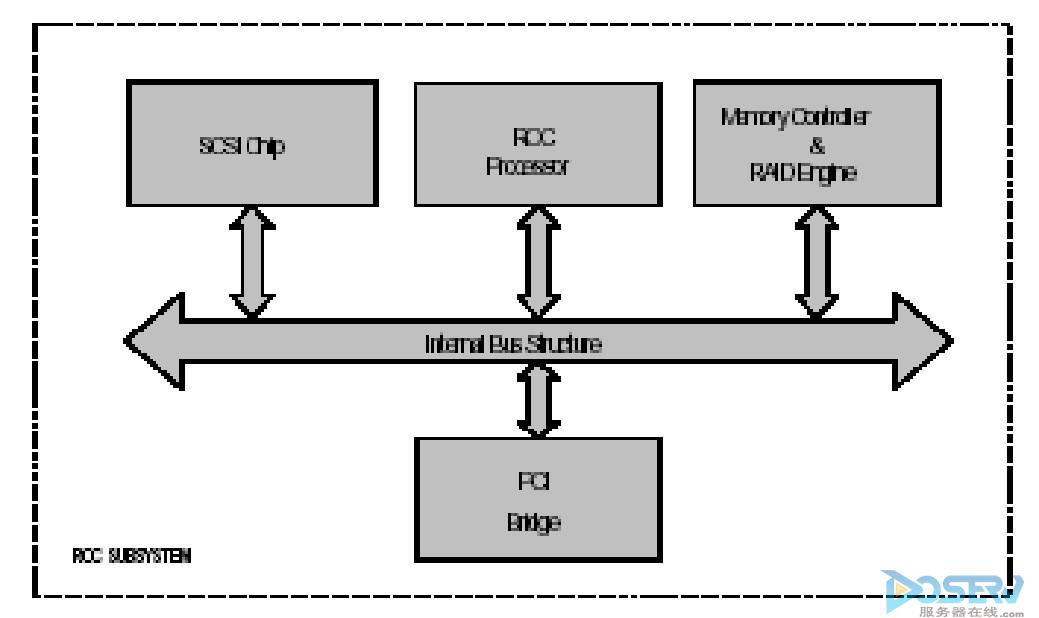

通过将一些不相关的组件进行组合并在一个集成电路中相连接,惠普公司开发了全集成硬件RAID解决方案。ROC 子系统包括处理器、内存控制器、硬件RAID引擎、SCSI芯片、PCI桥和一个内部总线结构,所有这些组件组成了一个单独的底层结构。

惠普公司 ROC 子系统简易模块图

处理器

在ROC子系统中控制RAID实现的ROC处理器采用的是ARM7 32位RISC核心。为产品特制的固件将信息由外部的只读闪存(ROM)读入ROC内存,并在ROC内部执行,该操作独立于主机处理器。在ROC子系统实现RAID功能时,主机处理器可以同时处理其他的事物。

SCSI 芯片

SCSI 芯片由两个内置Ultra-2 SCSI通道组成。其中一个用于支持服务器内置磁盘驱动器。另一个被用来对SCSI磁带机的支持。当支持设备为6个内置SCSI设备和一个SCSI磁带机时,SCSI芯片组达到其设计的最佳性能。虽然第二条通道可以不连接SCSI磁带机而是用来连接外置存储部件,但是增加的负载将降低整体 I/O 性能。如果要在外置存储部件存在情况下获得高的I/O 性能,惠普公司建议选用高性能的惠普 Smart Array Controller (惠普智能阵列控制器)来对外置存储系统进行支持。

PCI 桥

PCI桥提供了ROC子系统内部总线结构与服务器PCI总线之间的接口。主机处理器通过PCI桥与ROC处理器进行通讯。

内部总线结构

ROC内部总线结构由一些在ROC子系统内部组件之间提供通讯通路的内嵌总线构成。这个结构在密集环境中的处理器、内存和存储器之间提供高可靠性信息和数据控制。内部总线结构通过PCI桥与主机处理器相联接。

内存控制器和RAID引擎

ROC内存控制器采用内置接口与位于主板上的动态随机存取存储器(DRAM),闪存,和非易失性静态随机存取存储器 (SRAM) (图 10)相连接。RAID引擎控制RAID 5实现中的奇偶校验。

图10. ROC内存控制器与主板内存资源接口模块图。

SRAM

SRAM的使用取决于ROC程序代码。SRAM 是非易失性内存,其中存储着数据重构时子系统的状态。如果重构过程中电源失效,SRAM中的数据可使子系统由电源失效前的时间点继续重构进程。

闪存

闪存提供到主机处理器的初始代码以及到ROC处理器的程序代码。

DRAM

DRAM 被用于存储ROC程序代码和操作数据,同时作为前读缓存。

该缓存使用智能前读算法来预估所需数据以减少等待时间。它可以对单个或多个线程中的顺序读取操作进行跟踪并预先判断接下来的顺序读取操作。它可以在数据请求真正发生前,从磁盘中前读或预读出数据。而当数据请求发生时,从高速缓存中提取数据的速度将是从磁盘中毫秒级提取速度的几百甚至上千倍。

这种适应性前读设计对于小块顺序读取请求有着极佳的性能表现。同时由于在非顺序读取情况下前读机制被关闭,因此对于随机读取模式也没有不良影响。