随着4月19日亚洲大学生超级计算机竞赛(ASC13)总决赛落幕,中国大陆的清华大学代表队获得决赛总冠军,同时获得了最高计算性能单项奖,来自中国台湾的清华大学代表队获得亚军,来自大陆的华中科技大学代表队获得MIC应用优化单项奖。其中华中科技大学在基于英特尔集成众核(MIC)架构的英特尔至强融核协处理器上获得“MIC应用优化奖”成为一个亮点。

华中科技大学BSDE应用成绩突出

笔者与华中科技大学沟通了解到,华中科技大学对计算金融BSDE应用优化后,与优化前的CPU串行程序状态相比,性能实现了6万倍的提升,其中6万加速比的结果中有300多倍来自并行化、向量化、访存等优化,200多倍来自算法的优化,充分展示了对应用的深度了解。

华中科技大学获ASC13大赛MIC应用优化奖

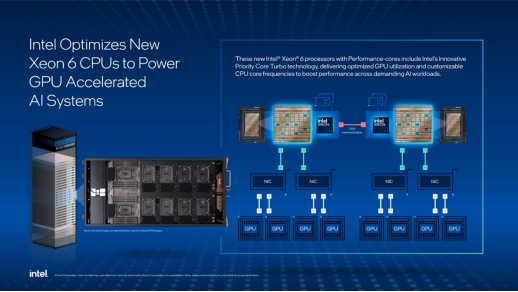

从规则来看,参赛队需要在3000瓦功耗限制下自行设计搭建超级计算机系统,并进行HPL、GROMACS、OPENCFD、WRF、BSDE 等5项优化测试,在方案和策略方面,不同高校代表队各具特色,构建的超算平台差异性很大,规模最大的采用了9个节点,最小的采用了4个节点,既有 CPU+GPU混合集群,也有全部采用MIC的众核集群,尤其是BSDE应用,其要求为基于单至强融核协处理器超算平台的应用并行化设计实现及性能优化。

华中科技大学决赛现场

笔者深入了解到,华中科技大学通过研读浪潮-英特尔中国并行计算联合实验室的《MIC高性能计算编程指南》,对英特尔集成众核(MIC)架构的特点和应用优化方法有了全面的认识,采用至强融核协处理器应用加速的实施:

在小规模算例上,采用在CPU上启动任务,将全部计算过程以offload模式交由英特尔至强融核协处理器完成的方案,对于大的算例则采用CPU与至强融核协处理器协同计算,通过offload signal/wait方式将一部分计算任务交由至强融核协处理器异步完成。

另外,对于不同方案之间的临界点,则根据现场实测结果用MATLAB进行曲线拟合分析得到。在以上方案的基础上,华中科技大学还采用优化数据访问方式、算法模型优化等方法加快应用运行。

此外,他们还将应用热点中的多次计算任务合并成一次计算任务,并提到循环外,避免重复计算,使用访存的时间代替计算任务执行的时间,大大提高了并行应用性能。

由此,华中科技大学取得的成绩表明对英特尔集成众核(MIC)技术理解,充分掌握了相关并行编程模式和算法优化技巧。基于英特尔集成众核(MIC)架构的加速技术具备高并行化和易上手的特点。