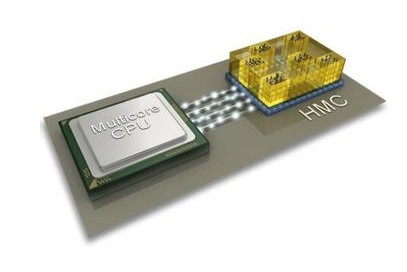

当前,随着CPU的性能不断提升,内存带宽成为计算机性能提升的瓶颈。一个解决办法就是将DRAM在逻辑层之上按层堆叠,从而使所构成的混合内存立方体(简称HMC)拥有更高的访问速度。近日,美光公司发布了这一构想的实现方案,向全世界公布了其专为千万亿次超级计算机所开发的HMC芯片。除了高性能计算机之外,这款新片的目标应用还包括数据包处理、数据包缓冲或存储以及处理器加速——总之任何在内存带宽限制方面受到束缚的应用都能从中获得提升。

HMC主要设计思路

一块DRAM芯片结合了访问流程所必需的内存与逻辑功能。如果大家将DRAM芯片层彼此堆叠,那么逻辑电路也将出现重复。HMC给出的方案是将逻辑电路从各DRAM芯片当中去除,使用一个位于芯片底部的基础逻辑层(Logic Layer),为DRAM层提供相应功能。

如果你见过Nvidia公司最近宣布的下一代(2016ish) Volta图形卡 (使用了一个堆叠的DRAM设计,据称可提供1TB/s的带宽),那么看到上图的HMC说明图,你或许会觉得有点眼熟。

该HMC方案当中拥有四到八个内存层,每个内存层都拥有数百万个处于定义组(仓库)中的内存单元,并配备复杂的支持逻辑(仓库控制器)、旨在全方位控制内存单元并提供面向内部通交叉交换机制的接口……HMC拥有16套彼此独立运作的仓库体系,目的在于让每个体系实现稳定的10GB/s(即80Gb/s)真实内存带宽。逻辑层还支持外部接口、交叉交换、内存调度器、内置自测试(简称BIST)、边带信道以及众多可靠性、可用性及可服务性(简称RAS)功能。

堆叠式芯片的几大难题

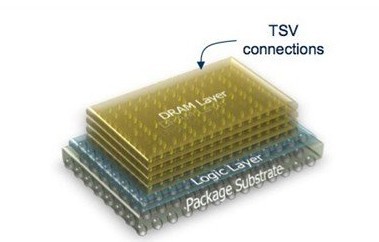

难题一:能够控制制造精度决定产品能否成功:逻辑层通过贯穿整套结构的通道实现与各DRAM层的连通或者对话,也就是所谓硅通孔(简称TSV)机制。这给制造工艺设计师带来了不少难题,因为用于连接底层与三层之间的硅通孔长度与用于连接底层与四层之间的硅通孔长度几乎没什么差别。控制制造精度成了产品成功的必要前提,因为一旦连通的层数出现偏差、整个多层模板就会彻底报废,由此带来的损失要远高于单层DRAM晶圆。

HMC的方案展示:利用硅通孔(TSV)作为贯穿各层的通道

难题二:硅通孔技术能否与自身经过的DRAM层绝缘:这些硅通孔技术必须完美地与自身经过的DRAM层相绝缘——这又是另一个制造层面的难题。

难题三:DRAM层在硅通孔贯穿位置不能存在内存单元。

难题四:层数越多,我们所需要的硅通孔数量也越多,这就让芯片层设计师的工作变得愈发复杂。

硅通孔让访问进入“大规模并行”时代

硅通孔则使访问进入“大规模并行”时代。HMC设备中的DRAM非常独特,其设计目的在于支持十六个独立的内存空间。每套内存空间提供10Gb/s稳定内存带宽,因此立方体的整体带宽可达到160GB/s。在每套内存空间当中,各DRAM层都拥有两个存储单元,相当于2GB设备中总计包含128个存储单元、4GB设备中总计包含256个存储单元。这给系统性能带来了巨大影响——与以锁步方式运行存储单元的常规内存相比,新方案拥有更低的查询延迟以及更出色的数据响应可用性。

美光公司还表示,其HCM的160GB/s带宽相当于DDR2模块的15倍,功耗则比现有技术低出达70%。它所占据的空间也比RDIMM低出约九成。

HMC生态系统

目前,HMC联盟共有八位主要开发成员,包括Altera、ARM、IBM、SK海力士、美光、Open-Silicon、三星以及Xilinix。HMC 1.0规格目前已经制定并正式公布,且拥有超过一百家企业计划采用这套方案。

这些企业能够利用HMC作为“近内存”,即将其安装在处理器附近;或者作为“远内存”,即使用向外扩展HMC模块以实现更高的能源效率。