2017年9月19日,“英特尔精尖制造日”活动在北京举行。

英特尔公司执行副总裁兼制造、运营与销售集团总裁Stacy Smith全球首次展示“Cannon Lake”10纳米晶圆,它拥有世界上最密集的晶体管和最小的金属间距,从而实现了业内最高的晶体管密度,领先其他“10纳米”整整一代。

10纳米中国首发,技术领先

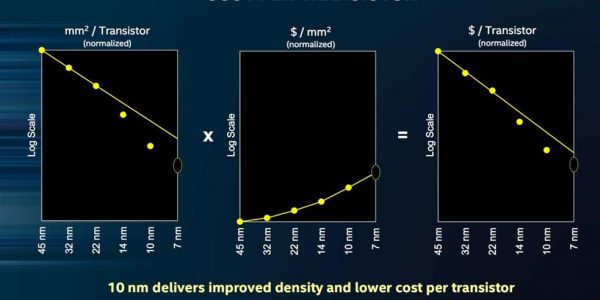

英特尔10纳米工艺采用第三代 FinFET(鳍式场效应晶体管)技术,其使用的超微缩技术(hyper scaling),充分运用了多图案成形设计(multi-patterning schemes),助力英特尔延续摩尔定律的经济效益,从而推出体积更小、成本更低的晶体管。英特尔10纳米制程将用于制造英特尔全系列产品,以满足客户端、服务器以及其它各类市场的需求。

英特尔10纳米制程的最小栅极间距从70纳米缩小至54纳米,且最小金属间距从52纳米缩小至36纳米。尺寸的缩小使得逻辑晶体管密度可达到每平方毫米1.008亿个晶体管,是之前英特尔14纳米制程的2.7倍。

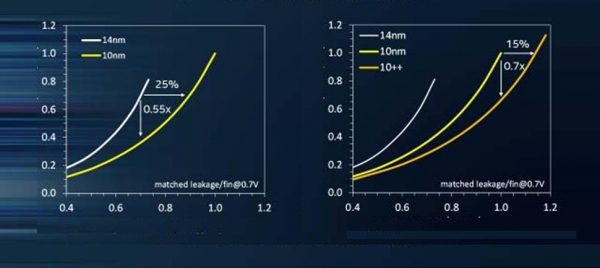

相比之前的14纳米制程,英特尔10纳米制程提升高达25%的性能和降低45%的功耗。增强版的10纳米制程可将性能再提升15%或将功耗再降低30%。

英特尔晶圆代工业务通过两个设计平台——10GP(通用平台)和10HPM(高性能移动平台),向客户提供英特尔10纳米制程。这两个平台包括已验证的广泛硅IP组合、ARM库和POP套件,以及全面整合的一站式晶圆代工服务和支持。

英特尔创新技术研发前瞻

纳米线晶体管被认为是未来技术的一种选择,因为纳米线的结构可提供改进通道静电,从而进一步实现晶体管栅极长度的微缩。

硅是MOSFET通道中经常使用的材料,但是III-V材料(如砷化镓和磷化铟)改进了载流子迁移率,从而提供更高的性能或者能够在更低的电压和更低的有功功耗下运行晶体管。

硅晶片的3D堆叠有机会实现系统集成,以便把不同的技术混装到一个很小的地方。

多种不同的高密度内存选择,其中包括易失性和非易失性存储技术,正在探索和开发中。

对于精尖制程技术来说,微缩互联和微缩晶体管一样重要。新的材料和图案成形技术正在探索中,以支持高密度互联。

极紫外(EUV)光刻技术:采用13.5纳米波长。由于当今的193纳米波长工具已达到其微缩极限,该技术正在研发中以实现进一步的微缩。

自旋电子是一种超越CMOS的技术,当CMOS无法再进行微缩的时候,这是一种选择,可提供非常密集和低功耗的电路。

神经元计算是一种不同的处理器设计和架构,能够以比当前计算机高得多的能效执行某些计算功能。

大举进军代工市场

自2008年推出单个22纳米技术平台产品以来,英特尔晶圆代工业务不断发展,为客户提供高级技术与IP,以支持最为严苛的世界一流设计的实现。

英特尔晶圆代工业务基于其先进的22纳米、14纳米和10纳米技术,提供了完整的一系列平台。这些平台构建于英特尔全球领先的制程技术之上,在过去15年来引领了行业创新。此外,代工业务生态系统为这些平台提供全面的支持,包括完整的行业标准IP组合以及经过认证的电子设计自动化(EDA)工具流。

目前,英特尔提供多种最先进的半导体技术平台,包括旨在向所有市场普及FinFET技术的全新22FFL平台,以及能够为行业带来最佳功耗、性能和面积(PPA)的最先进、最高性能的10纳米技术等。此外还提供领先的差异化IP,如56Gbps PAM4 SerDes和创新的EMIB等。EMIB提供了卓越的2.5D封装能力。

所有这些技术均通过一个垂直集成的“一站式商店”交付,不仅能够确保为客户带来协同优化程度最高的平台技术和IP,以及卓越的质量和可靠的制造服务,同时还让客户可以使用到全面集成的封装、装配与测试服务。