7月20-21日,2018全球存储半导体大会暨全球闪存技术峰会(简称“GSS大会”)在武汉光谷拉开帷幕,大会以“构建闪存新生态”为主题,针对全球闪存和存储半导体的产业新生态、行业新热点、企业新发展,进行全面分析与解读。

上海威固首席科学家,技术委员会主任李礼发表了题为《威固存储控制器自主可控之路》的主题演讲。

以下为速记部分内容,未经演讲人确认:

研制自主可控控制器芯片的必要性显而易见,首先是信息安全。我们总结了一下,可能存在的后门漏洞有以下四种,其中前两种可以说是主观无恶意:

第一未公开的自定义调试接口,比如去年10月份新闻报道的台湾某主控厂商的问题,站在中立角度来说,这可能是竞争对手的中伤,因为后门漏洞是一把双刃剑。话说回来,站在部门主管的角度看,没有公开的自定义调试结构是掌握在华为手中,还是掌握在英特尔手中显然是不一样的。

第二是体系结构漏洞,今年1月份媒体爆出的英特尔体系结构BUG,Meltdown熔断、Spectre幽灵,主要是高性能处理器里面有分支预测、超标量这些经典的技术,有几十年的历史了,我们突然发现原来这些技术里面都存有BUG。

第三是固件代码植入后门程序。存储设备是被动的,有观点认为只要上面的CPU安全,就是安全的。现在我们举一个反例,1990年的伊拉克战争,美军通过称为被动设备的打印机让伊军的控制系统感染病毒并最终瘫痪,还有一种说法,主控芯片是封闭的,上面没有跑应用程序,2010年伊朗政网系统是核工业体系上的一个封闭系统,但美国通过政网系统使其核工业体系瘫痪。

第四个风险是硬件木马风险,在芯片设计中植入某些特殊的电路模块,在一定时期会得到触发。甚至现在有报道,不仅是在设计过程中,就是芯片的制造过程中也有办法植入硬件木马,所以安全问题是防不胜防。

第二是产业安全,不得不提到前一段时间的中兴事件,中兴在交了巨额罚款以后涉嫌过关,突显了产业安全必须要有高端的、自研的控制器芯片来适配。

威固作为一家新兴的公司,在自主可控的浪潮中,我们一方面不妄自菲薄,另一方面也要有的放矢,所以我们的发展思路,第一是分阶段逐步实现不同程度的自主可控,我们看来是分为五大阶段:

一是自主可控的固件与驱动,实现功能层面的自主可控;

二是自主设计的SoC架构,实现性能的自主可控;

三是使用国产处理器核心,我们不是使用ARM的处理器核心,而是采用国产处理器核心来研发控制芯片,并对国产的主处理器芯片适配,达到软硬件系统的自主可控。而威固公司正是处在自主可控的第三阶段;

四是采用国内工艺,是国产的闪存介质,高速接口等,实现与产业链上下游合作伙伴的自主可控;

五是参与国际存储行业标准制定,并作出相应的贡献。

第二个发展思路,“通专”结合,军民融合。通是高端通用存储器芯片,我们是本着十年磨一剑,要持续发力,以开发高端通用存储控制器芯片作为能力牵引。超算芯片最能体现一个国家的综合国力,高端存储控制器芯片也最能体现一个公司的实力。专是指专用定制芯片,我们想针对自主可控需求非常迫切的领域研发定制芯片,因为通用存储器芯片已经是一片红海市场,包括SoC芯片的开发门槛也在逐步降低,所以我们就要走专的路线。专的路线相对来说比通的东西要简单得多,但是往往需要很多特色,实现的效果也会比较好。

威固在定制芯片方面有三个方向,第一是拟态安全存储控制器芯片,一般说就是和加密、解密相关;二是宇航级存储控制器芯片,比方说火箭上使用的;三是针对雷达信息采集的专用存储控制器芯片。

下面简要介绍一下通用存储控制器芯片的研发历程。

第一代产品代表为“秦”,技术源于美国BitMicro公司。2014年完成引进,经过消化吸收,于2015年底流片。采用90纳米境外工艺,处理器核心和原有工艺一样,采用了Synopsys ARC750D 处理器。

第二代控制器为“唐”,2016年1月开始研发,2017年3月完成设计和流片,前端都是资深设计完成,已经完成了与国产处理器申威的适配,这是技术特征,主要是基于28纳米的境外工艺,采用ARM处理器核心,上面跑的是NVMe协议。

第三代存储控制器“宋”正在研发,从去年年底开始,这个项目受到国家“核高基”项目支持,采用“中国心”——高性能4核“申威”处理器核心,处理器是上海高性能集成电路设计中心具有完全自主知识产权的国产高性能处理器核心,以IP核方式授权使用。采用了完全自主设计,PCI-E 3.0 X8接口并遵循NVMe1.3协议,同时集成有PCI-E 3.0 RC接口便于进一步扩展。自主可控的好处在于,处理器核心代码是自己写的,我们一旦发现漏洞,设计人员就有可能对代码进行修改,这也是自主可控最核心的能力。这款芯片是为超算应用量身定制的,

定制存储控制器研发情况。军工、航天等特殊领域对存储控制器芯片有不同于消费级、企业级市场的特殊需求,性能要求不需要特别高,介质基本上是不用的,地面上大部分用的是MLC,天上用的是SLC,但是对安全性、可靠性有很大的需求,包括不同的应用内存缓冲特征也和消费级、企业级有很大的不同。达到高安全性、高可靠性,或者是高能耗比、小型化的需求。

首先介绍下拟态安全存储控制器芯片,因为是党政军的办公系统对密码计算的安全性有很高的要求,密码计算仅仅是一部分,首先要求密码算法是可重构、可二次开发的,比如中办、国药局这些部门密码算法都不允许厂商参与开发。

第二能防止基于时钟、电压扰动的主动攻击。一旦超频,大部分的路径都处在安全范围内,但是小部分的逻辑初衷不是按照设计者的初衷设计的,因此可能会出现代码跑偏的状况,给攻击者可乘之机。

第三防止能够基于时间的旁路攻击,能够防止基于能量耗散、电磁泄露的旁路攻击。

第四是能防止基于能量耗散的旁路攻击。攻击者分析能量、电池信息推测出密码芯片使用的密钥,针对以上需求我们开发了拟态安全的存储控制器,采用SATA3.0接口,国内处理器内核,通过拦截加固以及软件加扰方式,有效防止Cache旁路攻击,通过内置噪声源以及功耗平衡技术,有效防止电磁旁路攻击、功耗旁路攻击。

第五是通过嵌入式eFPGA技术,集成高性能可二次开发、可重构的加解密引擎,实现算法在线可重构,支持防御手段拟态变换的动态性、多样性。现在网络安全是防不胜防的,所以保护者要以一种无法判断的防御节奏,落实到芯片层面就是用嵌入式技术。

第二款是宇航级的存储控制器芯片。在太空环境下电子设备没有大气层的保护,会受到宇宙中高能粒子的辐射,造成工作的异常和故障。典型的有三个效应,第一是总剂量效应,高能粒子在晶体管的氧化层造成器件性能下降,甚至造成器件失效。第二是单粒子翻转效应,第三是单粒子拴锁效应。针对上述的三个效应我们采用全方位的抗辐照加固,第一是双活备份,第二是前端逻辑结构加固,第三是后端单元库加固,第四是封装加固。

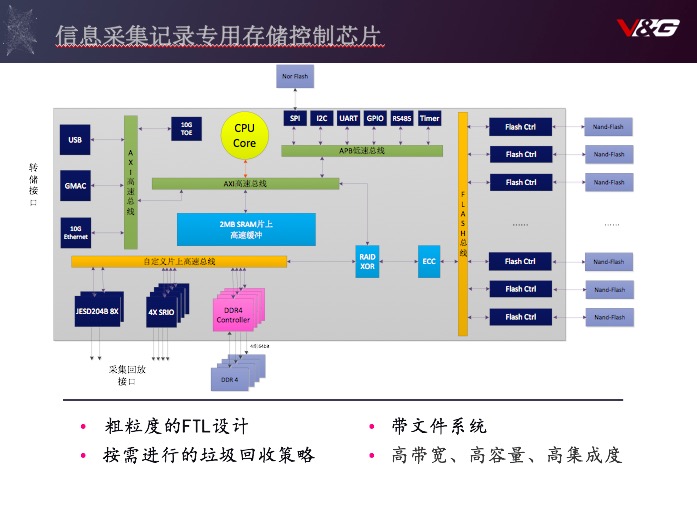

第三款是雷达信号采集记录专用存储控制器,首先我们需要真实的外场数据,比方说预警机、空警两飞要进行一些信号采集,落地之后导出进行内场回放,便于雷达系统的研制。雷达数据采集特点第一个是采样精度要求高、采样率要求高,带宽需求很大,一个主控芯片要达到8GB/s以上。第二个是存储容量需求大,单板容量要超过32TB。第三个是需要长时间持续不间断无阻塞采样与存储,不允许出现短时间的掉速现象。第四个雷达信号峰值带宽有可能是平均带宽的6到8倍,需要无阻塞采样。第五是机载、舰载要求设备小型化。因为预警机上的空间都是寸土寸金的,然后针对这些特征开发专用控制器。

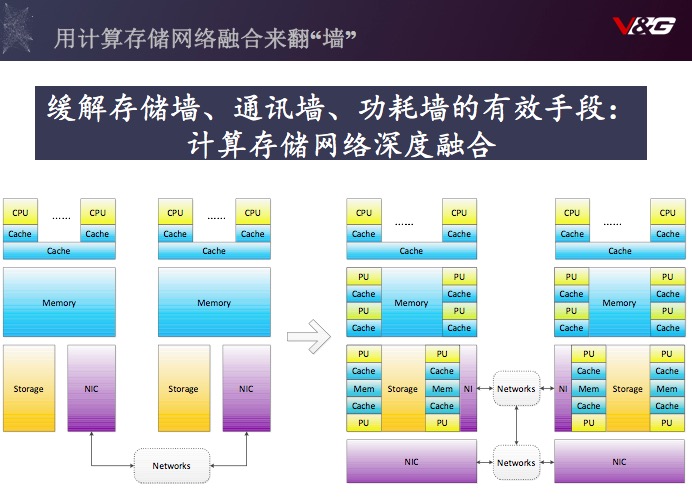

最后一部分我介绍一下计算存储网络深度融合控制器芯片原型系统。威固的计算存储融合主要不是在器件层面,而是在体系结构层面的微创新,左边的图是经典的冯·诺依曼的结构,我们下一代的体系结构可能变成右边的图,计算单位不变,但是在内存里面会有处理器单元,在存储中也有计算单元,同时有存储专用网络接口,这个专用网络接口不是整个计算机系统的网络接口,而更偏向于系统的私有网络接口。

威固认为未来控制器的特征,首先是三位一体,计算、存储、网络芯片的深度融合。第二能够包含多种异构计算匀速,比如多种计算形态将在芯片中并存。第三是Host CPU与存储控制器软硬件联合优化。第四是内存与外存的相融合。对于下一代计算存储融合我们首先推动的是在,落地后是一批全高半长PCIE存储卡,前端是采用PCLe 3.0 X4接口或SRIO2.0接口,4路高速串行接口,支持互联层各种网络拓扑,如Mesh网、Fat Tree,支持Host Based和FTL,最大运行功耗是60W。

这是威固在原型系统上自己开发的小demo,首先是带车牌识别功能的智能存储,可以支持后台自动完成车牌识别,识别的同时完成KV Store的构建,支持车牌反查图像,识别率99%,还没有达到商业应用五个9的要求,能每秒识别近千张车牌。

第二是计算融合雷达信号采集卡,预警机要飞到天上进行雷达信号采集,实际情况是数据量很大,但数据利用率比较低,可能32TB最后能使用的仅仅是一小部分,我们想把计算的功能融合在存储卡里面,比方说雷达信号处理的算法,有一些脉冲压缩、波束形成等,都可以集成到控制器里面。这些操作的好处是可以增加存储空间的利用率,增加处理的实时性。

以上就是我的分享,最后一句话是自主可控永远在路上,谢谢大家!