2019年1月8日,北京时间早8点,英特尔在CES上介绍了一些新方案,包括消费级以及数据中心处理器,人工智能,边缘计算等场景的方面内容。

10nm处理器?酷睿先行至强再等等

终于,英特尔也正式宣布了自己的10nm架构,按照惯例,消费端会先行一步,今年只会以Sunny Cove微架构出现在Ice Lake消费端产品上,不过,2020年才会用在至强处理器上。

这几年来,10nm可能是英特尔最不好意思谈的话题了。不过,这次发布终究开始谈到了10nm,采用10nm的除了上面提到的两类处理器,还有一个叫Lakefield的新产品(下文会详谈),以及一个Snow Ridge网络处理器。

Snow Ridge网络处理器家族是面向5G的无线网络设备做的,面向边缘网络节点,赋予边缘节点在计算、虚拟化以及人工智能方面的能力,看到这段描述,是不是感觉其定位跟Xeon-D处理器有些类似?

Cascade Lake处理器已经出货了。大概是在一年半之前,英特尔发布了第一代至强可扩展处理器Skylake-SP,下一代关于Cascade Lake-SP和Cascade Lake-AP的消息也不绝于耳,不过,这次发布透露出英特尔已经在出货Cascade Lake了,一部分客户已经优先拿到了生产品质的处理器,主要是AWS、Google、Azure和百度这样的超大规模数据中心。

有消息说,大概有一半的数据中心处理器都是英特尔直供超大规模数据中心,而不是通过分销商卖出去的,而且这部分处理器经常不出现在roadmap上,这些处理器的TDP会高一点,核数、cache、内存配置都可能会有所不同。

用于推理的Nervana AI处理器

英特尔推出神经网络推理处理器(NNP)Nervana,它是一种大规模的神经网络训练加速处理器,性能和功耗比CPU和GPU的表现都要好。今年可能会陆续有几次大的更新迭代。

通常对于处理器来说,人工智能的负载分两类,一类是负责训练模型,一类负责运行训练好的模型,后者就算推理(inference)负载,今年推出的Nervana是神经网络推理处理器。一般来说,训练的处理器要比用于推理的处理器规模大的多,为了性能和成本,通常都是分开做的,NVIDIA的处理器也是一样的策略。

英特尔在人工智能方面的芯片太多了,显卡GPU在并行处理方面有很大优势,在集中化的人工智能训练平台中,GPU非常合适,然而,在更多靠近数据的场景中,需要较低功耗较低成本的设备来提供计算能力。

英特尔通过一些列收购来构建AI芯片生态,Nervana的NNP算一个,Movdius的VPU(视觉处理)算一个,CPU也算一个吧,如果非要数清楚的话,做自动驾驶的Mobileye也算一个,另外,英特尔还计划在2020年发布自己的显卡。

CES的这次大会上,英特尔还宣布与Facebook一起研究Nervana,为什么是Facebook呢?

可能因为Facebook开源了PyTorch吧,谷歌开源了Tensorflow之后不是推出了自己的TPU吗。照这个趋势发展下去,人工智能的软硬一体优化可能会越来越流行,优化后肯定会比通用的GPU更便宜,功耗更低,性能会更强,当然,产品分类也会显得很凌乱,换个词儿,叫百花齐放各尽其用。

笔者比较感兴趣的还有这个Lakefield

代号为Lakefield 的方案展示出来的一块形状类似m.2 SSD的长条状卡,其实是一块微型主板电脑(听上去又有点像树莓派),板子上有一块10nm的Sunny Cove CPU,还有4颗Atom处理器,类似于平板手机里的协处理器的感觉,加起来一共有五个CPU,英特尔说这叫混合架构,然后可以提供低功耗计算、显卡和网络、I/O和内存资源。

这东西的应用场景能是什么呢?英特尔的人说,这是世界上最小的PC主板,现场展示的场景是用在平板电脑这样的低功耗设备上的,将来还能用到哪儿呢?可能是英特尔利用现有资源对抗ARM阵营的又一力作?先不猜了,这不是重点,重点它用到了叫Foveros 3D的封装技术。

Foveros 3D的封装技术

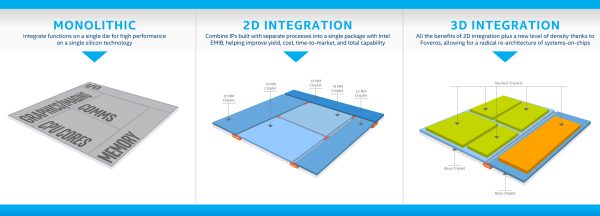

3D NAND自2013年以来话题热度逐步攀升,从2D到3D,堆叠的NAND芯片的存储密度得到了很大提升,随着工艺技术的日渐精进,单位容量价格越来越便宜,性能表现也不逊色2D产品,如今3D NAND已成主流。

有了3D NAND为啥内存不能做3D呢?内存可以的话,为啥CPU芯片不可以呢?近年来有不少人在设想和研究3D堆叠的内存技术,英特尔的Foveros 3D封装技术很有可能也是从3D NAND找到了灵感。

Foveros的思想也是把高性能、低功耗硅工艺技术的器件封装的更紧密,让高性能逻辑芯片也享受到堆叠的乐趣,比如CPU、图形芯片和人工智能处理器,让他们在单位空间内放更多的芯片,浓缩更多计算能力。

这样的新技术给芯片技术带来了挑战,同时也带来了方便,为IO或者别的各种资源提供很大的设计灵活性。其中 I/O、SRAM 和电源传输电路可以集成在基础晶片中,而高性能逻辑“芯片组合”则堆叠在顶部。

2018年以前是传统平面芯片设计,2018 年英特尔推出嵌入式多芯片互连桥接(EMIB)2D 封装技术,现在英特尔推出了3D Foveros堆叠封装技术,今年会有产品推出就是上面刚提到的Lakefield,未来会普及到更多产品线中,比如至强处理器。