下篇,作者从长远角度,对未来多核处理器的方向性问题进行了一些探讨,如片上SMP、异构多核、核心过多、内存带宽等问题。

1)在芯片上实现SMP系统(SoC,SMP on a Chip)

在上世纪90年代中后期,RISC SMP 市场的主流产品是 4路、8路 和 16 路系统。这些系统为当时的并行化应用提供了足够的CPU性能,价格也不算高。但现在,我们看到的趋势是,在未来数年内,有望在一块芯片上实现类似的SMP系统,从而挑战传统的RISC市场,对此,几个值得进一步探讨的方向性问题是:

在上世纪90年代,RISC SMP开创了UNIX服务器市场,那么,今天的多核芯片能否以同样的方式为并行软件创造出一个新的市场呢?

为了有效利用多核处理器芯片,系统架构或编程模式是否需要进行根本性的改变?或者说,在适当增强架构的情况下(如transactional memory),并行应用市场能否实现自我增长?

对于绝大多数用户而言,随着芯片上的核心数、可执行的线程数越来越多,还需要更大规模的多路SMP系统吗?

事实上,随着每个芯片上集成的内核数越来越多,用户甚至在单路或双路服务器上,就可以同时混合运行多线程任务和单线程任务??无论是单线程,还是多线程应用,都不会独占全部的CPU核心??这种模式类似于最近10年来大型SMP服务器的应用。另外,CPU核心数的增多,也会促进虚拟化在这些低端多核服务器上的普及应用??每个客操作系统拥有自己专用的核心,同时争抢内存空间、内存带宽、共享缓存和其他共享性资源。

2)CPU设计时有更大的灵活度

随着CPU生产工艺的发展,我们可以在一个芯片中放入越来越多的核心,CPU的设计空间也越来越大,但选择多了,决策也自然就更难了。

双核处理器起初量产时,采用的是90纳米制造工艺,到今年,四核处理器开始采用65纳米工艺。而如果进一步向45 纳米切换,我们能把CPU中的核心数增加一倍(8核),采用32纳米,可望继续增加一倍(16核),未来,通过22纳米工艺再增加一倍核心数量(32核)也是切实可行的。

最近的研究表明,无论是从工程设计的角度,还是从应用性能的角度来看,CMP的设计空间都是多维的,有很多种选择。但问题是,由于一个芯片上拥有如此之多的独立“模块”,虽然我们在设计时的灵活度大大提高了,但同时,对性能和性价比指标的考量也就变得更加复杂了。如果每种应用对单线程性能、多线程性能、单线程性价比和多线程性价比都有不同的最优设计方案,那么,要想做出正确的设计决策将更为困难。对于产业界来说,是生产可以量产的标准化产品,还是在某一方面表现最优的独特性产品,将是非常关键的挑战。

3)异构多核芯片中不仅有CPU,还有GPU

术业有分工,对于不同类型的工作负载来说,同构(homogeneous)的多核芯片并不是最好的选择。而实际上,随着设计空间的扩大,我们可以在芯片中放入异构(heterogeneous)的处理器内核,这些不同的内核可能在以下这些参数上有所不同,如基本 ISA、ISA 扩展、缓存容量、频率、Issue宽度(Issue width)、乱序功能(Out of Order capability)等。

可见,这种自由度更高的设计带来了无数的可能性,既令人兴奋,又让人畏惧。

当然,多核心处理器将不限于仅包含中央处理单元(CPU)。随着3D图形处理卡在移动、客户端和工作站系统中的广泛应用,进一步将图形处理单元(GPU),或GPU的一部分功能集成到处理器芯片上也是自然而然的,就象AMD 已经发布的“Fusion”计划一样。在未来,其他的异型(非CPU)架构也是合乎逻辑的选择。

4)核心过多带来的问题

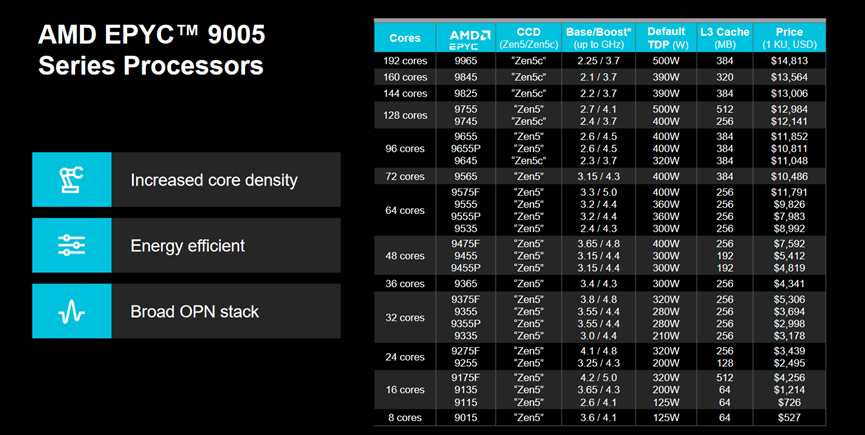

短期内,在每个芯片上集成4-8颗CPU内核确实非常让人兴奋,但从长期来看,如果继续在每个芯片上集成32、64、128、256个甚至更多的核心,就会带来额外的挑战。

拿RISC来比较,上世纪90年代后期,RISC SMP 市场正是鼎盛的时候,大型系统(8P-64P)的成本非常昂贵,占有的市场份额也很少。单个用户基本不用担心找不到足够多的工作使 CPU保持忙碌。相反,未来的多核处理器芯片不会很贵。一个用户能够轻松地负担多个CPU核心,足以满足传统“任务并行化” (占用CPU运行独立的单线程任务)应用所需要的CPU资源要求。

比如,在2004年,一台满配的基于 AMD 或英特尔单核处理器的双路服务器售价一般为 5000 – 6000 美元,拥有5万美元预算的一个科研人员/工程师,可以购买大约 8 台这样的服务器(即总共有16 个核心),加上一些存储和网络设备。其实,从2000年左右起,这类系统就开始大面积流行起来,许多用户发现,采用这些系统构成的小规模集群就能满负荷地运行串行作业,或者在一台服务器上运行并行化的应用(使用 OpenMP 或explicit线程)。

如果双路服务器配上16核的CPU,那么,在相同售价和预算的情况下,上述用户买8台服务器就可以拥有多达256个核心。而实际上,却很少有哪个科研人员/工程师有足够多的独立作业需要用到它。如果配上128核的芯片,那么,这8台服务器将能执行2048个线程。可见,对于绝大多数用户来说,编程模式和使用计算机的方式都要发生根本性的变革。

因此,多核处理器开发人员的任务很艰巨,他们必须找到可行的方法,以更容易地利用这么多核心来加速单一作业的效率。对于计算机用户来说,也同样存在巨大的机遇,如果能先于自己的对手充分开发这种并行化机制,就能获得更多的竞争优势。

5)内存带宽是多核系统的瓶颈

多核CPU设计的灵活度,以及功耗的减少,使得未来的处理器能比现在芯片具有更强大的计算性能。但另一方面,相对处理器的性能增长速度,内存带宽的提升要慢的多。虽然DRAM 技术通过提高管线能力(pipelining)从根本上改进了内存性能,但这种方法也快要走到头了。而且,在系统电力消耗水平中,内存的功耗也已不容忽视。

历史数据表明,如果一个系统,每GFLOP/s峰值浮点运算所支持的主内存带宽小于0.5 GB/s,就很难在市场上获得成功。比如,一个CPU芯片的峰值要想达到100 GFLOPS并非遥不可及??拥有8个核心,主频为3GHz,每个核心每个时钟周期执行4次浮点运算就可以了。但另一方面,要想为这样的每个处理器芯片配备50 GB/s 的内存带宽,却要花费巨大的成本。即便DDR2/3 DRAM 技术能提供1600 MHz的数据传输率(每个 64 位通道 12.8 GB/s),要想维持上述内存带宽水平,就需要许多通道??102.4 GB/s 峰值带宽大概需要 8 个通道,这就意味着至少需要8 个 DIMM,并需要丢弃类似 40 个出色的缓存,以实现 50% 的利用率。(若内存延迟为 50 ns,则 102.4 GB/s 的延迟带宽为 5120 字节,或每 64 个字节延迟 80 个缓存线。所以,共需要约 40 个并发缓存线,以保持 50 GB/s 的目标带宽。)

5. 总结与结论

本文的文字与图例说明,在多核心处理器带来的巨大机会和挑战面前,我们才刚刚开始。AMD最初的前进步伐一直受到技术的限制,只能对系统的整体平衡做有限的提升,但是,技术的发展趋势使AMD清楚地看到,未来工艺技术所提供的灵活性将给业界带来大量机会,使AMD能够设计出在功耗、性能和成本特性方面有显著提高的基于微处理器的系统(例如Barcelona和Fusion)。

对于计算产业而言,通过生产标准化的产品来保持高产量,通过创建种类丰富的产品来提高性能、每瓦性能和性能价格比之间的相互牵制,将成为整个行业的主要挑战。即使我们试图保持适度数量的“快速”核心,工艺技术也将支持我们提供超过用户当前的有效使用能力的核心。这将需要整个产业、学术界和计算机用户共同合作,开发出新的方法,能够利用多核心完成“日常”应用,利用片上通信的物理位置实现前所未有的、耦合更为紧密的并行机制。

资料:加速系数与Amdahl定律

衡量多处理器系统的性能时,通常要用到的一个指标叫做加速系数,定义如下:

S(p) = 使用单处理器执行时间(最好的顺序算法)/ 使用具有p个处理器所需执行时间

Amdahl定律的传统方程式表示方式:

S(p) = p / (1 + (p-1)*f)

其中 S(p)表示加速系数

p表示处理器的个数

f表示串行部分所占整个程序执行时间的比例

当f = 5%, p = 20时, S(p) = 10.256左右

当f = 5%, p = 100时, S(p) = 16.8左右

关于作者:

http://home.austin.rr.com/mccalpin/

第一作者曾在SGI和IBM工作,从事过Power家族的研发,也是Stream内存带宽基准测试的发明人,被同行昵称为“带宽博士”。曾多次代表IBM就Power接受媒体采访。

http://www.alliacense.com/Licensing_Charles_Moore_Biography.aspx

第二作者是多核心编程语言的发明人,具有数十年的业内经验。就职于AMD之前曾在多家公司任技术部门要职。

第三作者是AMD的CTO。