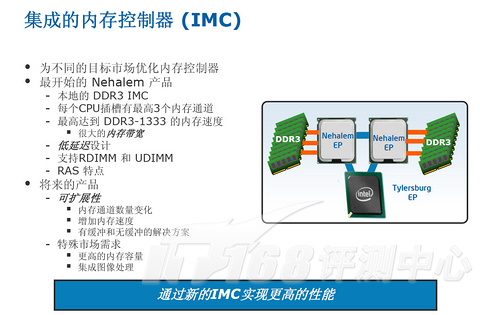

集成内存控制器

很久很久以前,在一个记忆体短缺的时代–不仅仅处理器外面记忆体很少,处理器里面也是。使用了CISC架构的x86处理器里面只有8个GPR通用寄存器(一般的RISC处理器有32个以上的通用寄存器,现在的x86-64有16个通用寄存器),由于通用寄存器数量上的短缺,因此不像RISC处理器那样,CISC的x86处理器使用了堆叠运算指令,也就是将运算结果保存在源寄存器上的,如ADD AX,BX指令会将AX寄存器与BX寄存器的内容相加,并将结果保存到AX上–这样对比于使用三个寄存器做同一运算的被堆叠指令RISC架构就节约了一个寄存器,然而相应地源寄存器的内存就销毁了。x86架构需要执行大量的Load/Store微指令(Pentium Pro开始具备)来进行寄存器-内存之间的存取操作。RISC处理器当中,Load/Store操作也很频繁。

2006年进行的一个研究当中表示,最常用的20条x86指令当中:

mov占35%(寄存器之间、寄存器与内存之间移动数据),push占10%(压入堆栈,也经常用来传递参数),call占6%,cmp占5%,add、pop、lea占4%(实际计算指令非常少)

mov、push、pop都是和load/store直接相关的,add、cmp等则间接相关

顺便:

75%的x86指令短于4 bytes,也就是小于32 bits。不过这些短指令只占代码大小的53%–有一些指令非常长

单操作数指令占37%,双操作数指令占60%

双操作数指令中,直接数操作20%,寄存器操作数56%,绝对寻址操作数1%,间接寻址操作数23%

现在来看这样的设计简直是无法想象,不过这样脑残的设计不仅仅用到了今天,而且还加速到了一个不可思议的境界……在与各种RISC架构处理器的交锋也不落下风……回到架构上,由于x86架构实际上是通过耗费寄存器-内存带宽来节约寄存器数量,大量的Load/Store操作(Load操作占据了x86 uops当中的约30%),对缓存乃至内存的性能非常依赖。

Nehalem具有三个Load/Store单元以及一个MOB架构,并支持内存数据相依性预测功能,缓存性能非常出色

缘此,x86架构在缓存-内存上的提升是不遗余力,不提2008年度评测报告:深入Nehalem微架构中说到的内存数据相依性预测功能(Memory Disambiguation),对于Nehalem而言,这方面最大的改进就是直联架构带来的IMC集成内存控制器,它使CPU到内存的路径更短,大幅度降低了内存的延迟,同时每一个CPU都具有自己专有的内存带宽。这一点在数据库应用中表现非常显著,数据库应用对存储器的延迟很敏感。

AMD使用了集成内存控制器的Operton在推出之后,立刻占据了不小的市场份额。Operton自然也属于x86架构的处理器,因而可见存储子系统对x86架构影响之巨大。

直联架构还隐含的一点是,去掉了FSB(或类似总线)对内存存取的限制,FSB时代,存取内存需要处理器经过FSB总线访问MCH,再访问内存–而FSB总线已经限制了内存带宽的提升。在使用IMC之后,Nehalem的内存控制器立刻提升为三通道(每处理器),同时不同的处理器都具有独立的内存带宽。