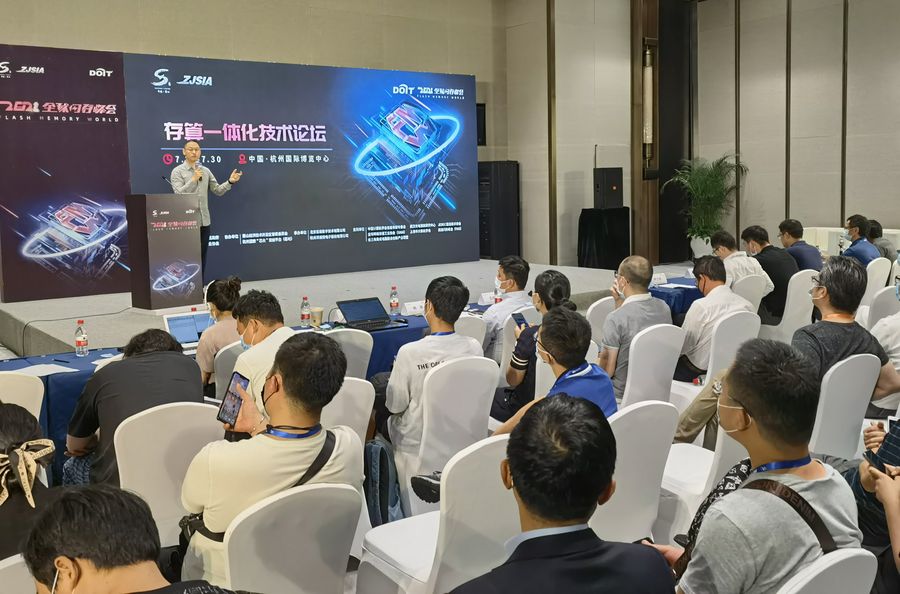

2021年7月30日下午,在杭州国际博览中心举办的2021全球闪存峰会上,堪称“中国首个专门针对存算一体化进行探讨”的论坛“存算一体化”成功举行。

知存科技创始人王绍迪,作为百易传媒(DOIT)特邀嘉宾和论坛出品人荣誉担纲主持人,并发表精彩演讲。

据了解,存算一体技术是最近几年才出现的一种新的架构。

在未来10年、20年,由于很难再看到摩尔定律持续向前发展,很多新技术的瓶颈无法再通过摩尔定律以缩小芯片尺寸工艺解决问题。比如做大算力,数据量很大的运算的时候发现,存储器和计算之间的数据瓶颈占了资源运算90%以上,而运算过程中传感器和芯片的数据通路占了其他90%以上的运算资源、运算时间、运算功耗。也就是说,在先进工艺的情况下,运算瓶颈不再是计算本身,而是在各个不同模块之间的数据搬运上,比如传感器到存储器到存储机到计算单元都有各种的数据瓶颈。

这种情况下,存算一体和感存算一体应运而生。

存算一体和感存算一体作为新型架构,是非常前沿和个性的技术,需要产业和学术界共同推广和发展。最近一两年内,很多的创业公司以及大公司进入这个领域,也为未来十年二十年以后的主流存算一体和感存算一体做了非常好的铺垫,更多公司上下游协作将会完成这样的壮举。

以无限算力改变世界:后摩智能异军突起于存算一体解锁超大算力

后摩智能联合创始人兼战略及市场、商务副总裁项之初以“无限算力 改变世界——存算一体解锁超大算力”为题,介绍了后摩智能以及近期从事的超大算力方面的研究。

算力是国家之间的战略级别的竞争,代表智能水平的指标是TOPS,接近通用人工智能水平的数值是5000TOPS。国外领先企业从2018年的1TOPS发展到今天已经254TOPS,两年后的下一代芯片将会达到1000TPOS。

算力正在快速增长,越来越接近人类的认知。面向这个拥有万亿级规模的广阔市场,后摩智能也提出了这样的目标。

为什么要涉足存算一体?后摩智能的信心从何而来?后摩智能联合创始人、战略副总裁项之初进行了阐述。

存算一体技术是最近几年才出现的一种新的架构。据项之初介绍,存算一体及其优势在于以下三个方面:一是存算一体功耗低。有数据预测,全球数据中心2025年的耗电量将达到总耗电量20%,而L5级无人驾驶所需的4000 TPOS算力水平,一年需要3万多亿度电,占全球发电量12%。又如AlphaGo下一盘棋打败了人类,但人类只用了20瓦的大脑能耗,而AlphaGo是2万瓦,这还不算无数的传感器都与数据加总支持的算力所耗费的能量。只有低功耗基础上的大算力才是可持续的,这也是国际国内共同关注的话题。二是存算一体减少了数据迁移,降低了延时。在自动驾驶赛道,低延时可能意味着挽回生命。三是存算一体做大算力芯片可以更简单,它的工程不像原来冯诺伊曼存储和计算分离架构下总线结构复杂相连。国外龙头企业团队实力雄厚,研发时间长,积累了强大的工程经验,形成了知识产权壁垒。采用同样的技术路径,直道追赶极其困难,而存算一体绕开了巨头壁垒,实现换道超车。

后摩智能是一家在南京、上海、北京都有研发中心的,年轻但实力强大的公司,其研发能力覆盖从存算一体底层的器件层,电路设计到架构全栈:在AI Core设计方面,有20年设计经验;在SoC层级,涉足从0.18微米和6纳米芯片;软件编译器、AI算法到应用场景有全栈的成熟和丰富的经验。基于自主研发的存算一体和先进工艺,面向无人终端以及边缘及云端的训练和推理打造出效率高出10倍乃至数10倍以上的算力芯片。

项之初认为,存算一体大算力芯片潜在的市场有两个:边缘端的推理和云端推理市场。无论是边缘端的推理和云端推理市场,它们共同的痛点都是散热和功耗。在数据中心,如果功耗降到1/10,可以多插90%的卡,那数据中心的计算密度就会成倍增加。这正是存算一体的芯片竞争力:大算力的芯片可以提升无人车和机器人的智能化,芯片的高能效比可以降低成本,满足散热等需求,甚至提升安全性。

可以说,AI时代为很多公司用另外一种方式超越国际领先水平提供了机会。

感知世界,倾听未来: 每刻深思的近传感模拟计算芯片

在传统的方案里,手机CPU里面都有一个功能一直开着的,可以在前端链接各种不同的传感器进行大量的监测和交互,比如语音的识别和唤醒,触觉视觉,但它最大的问题是因为它的主频率一直开着,所以对整个系统产生数量级的功耗需求。

采用近传感计算方式,意味着可以把功耗降低50到100倍,可以支持更多的应用。总体而言,带来的是1/3以上的成本下降。

这就是每刻深思最独特优势的技术——近传感模拟计算架构,最大化模拟计算功耗,消除了边缘计算中,除了存储器和处理器之间的瓶颈、传感器和计算芯片之间的瓶颈,还降低了把数据从传感器迁移到到处理器过程中能量的损耗。

2012年成立以来,每刻深思不断基于具体的场景为手机厂商,传感器厂商设计芯片,今年第一季度做了一款数模混合、直接面向客户IoT应用需求的MKA1031芯片。每刻深思CEO邹天琦表示,公司面向多传感器集成的通用模拟计算IP平台,其技术优势极具竞争力:

一是支持不同的传感器的集成。为了做到这一点,每刻深思把自己平台分为三大计算平台,其一是基于连续时间信号处理的TDSP平台,无论是做音频还是做加速度传感器,连续时间信号都可以在该平台上处理;其二是阵列信号SDSP平台,可以处理ToF、毫米波在阵列信号,其三是在2019年验证过的Fusion的平台,可以把前面两种信号在一款芯片上实现。另外,每刻深思还提供了完整的SDK工具,以使得用户可以很好的沿用以往的使用习惯来开发他自己的算法、进行参数的调优。当然,这个SDK同时是支持传统的MySQL算法与大部分DNN深度学习。

第二大优势是可拓展性,为将来往大算力场景扩展做好准备,第三大优势就是大幅降低功耗,这是解决客户最核心的痛点的特性。

谈到每刻深思未来的规划,邹天琦表示计划分三步走:明年客户基于Q4流片小规模量产,之后基于两种产品形态不断推高出货量,到2024年达到月出货量超过3KK的目标,实现亿元营收;到2026年之前以两种产品形态复制和应用到大量的场景,实现规模化的应用。

每刻深思在视觉领域也展开了大量的工作,在光学处理过程中加载了基于阵列信号的处理,在2019年把连续时间信号和纠正时间信号两种类型都融合在一块芯片上,实现了融合感知。

“希望和各位一起合作建立全时域智能感知服务平台,整合产业上下游,充分挖掘数据的价值,解决信息安全和隐私问题,以更低的成本服务于我们的客户。” 邹天琦说。

感存算一体:犀灵视觉的智能视觉传感器

犀灵视觉致力于智能视觉传感器开发,以解决感存算一体的问题,在智能视觉方面有很深度的积累。通过图片传感器上增加运算功能,使得传感器能输出精简关键的信息,直接输出神经网络推理结果,帮助整个AI提升运算效力。犀灵视觉核心技术包括矩阵式CMD、处理单元、感存算一体等业界领先的关键技术,实现高速与低功耗的芯片,芯片将于2022年2月份实现产品量产。

犀灵视觉创始人冉亮在演讲中指出,将传感、存储、运算都放在一起的感存算的架构,解决了两个问题:一个是冯诺伊曼架构的数据来回搬运的功耗瓶颈,因为和传感部分是一体化的,所以同时也解决了传感器本身和边缘AI之间的传输速度的瓶颈,实现超高速以及超低功耗的运行能力。

一个用180纳米做的芯片,处理器的像素量65536,虽然是比较老的工艺节点,但是性能也可以每瓦535GOPS的算力,这个算力不能和AI芯片的算力划等号,但和28纳米的处理器做的简单的手写字符的神经网络的对比可以看到,推理的时间和推理的功耗数据并不差,体现了这样的架构的处理优势。

另外,犀灵视觉支持的算法比较丰富,包括计算机视觉算法CV和卷积神经网络(CNN)算法,都可以在这样一个阵列式的上面来实现。

目前的应用场景比较丰富,包括手持的设备,家用的监控机器人、工业相机以及自动驾驶,都有一些意向客户在做前期的算法开发。

“经常会有投资人或者客户提出把边缘AI一起做进去。考虑到自己定位于一个传感器的公司,以超低功耗、超高速以及超高效率的特点来解决专门应用场景的问题,不一定要把所有事情都包在传感器上做,这并不是我们的目的。” 犀灵视觉创始人冉亮 说。

谈到后续的规划。目前第一颗产品还是用平面式的工艺,感光以及运算都在一张晶圆上。今年年底量产产品会用堆栈式的方式,也就是说上面是感光、下面是运算,通过堆栈式的方式来做芯片。这样芯片的尺寸会做的比较小,分辨率也可以做得相对高一些。后续技术扩展性也比较高,可以通过用不同的memory的介质做新的存和算,以及加一层硬件加速,来完成更多更加复杂的任务也是有可能的。远期也在关注光子运算、类脑等一些未来的技术。

在传感器上来做运算,业界蛮多公司都在做,刚才提到AISTORM是美国加州自一家公司,他们也在传感器上做运算,我们和他们不一样,我们是用电流做运算,他们是用电荷做运算,他们分辨率做不上去,但我们可以一直往上做,没什么问题。所以我们认为今后带一定智能运算的传感器应该更加大有可为。

存算一体化的路径及知存科技的WTM2101存算一体芯片

从事存算一体、感存算一体,起步很早,但最近几年才开始真正做产业化,原因也是这些技术都涉及到模拟计算、存储器这两大难题,最重要的是在芯片设计中没有针对存储器、模拟计算很标准很成熟的经验和工具去快速实现存算一体、感存算一体以及模拟计算。

知存科技创始人、CEO 王绍迪介绍说,公司创始团队2012年开始做存算一体技术,2016年完成7次流片,完成国内第一个基础FLASH存算一体的芯片验证,有了第一个验证成功的成果,但距离产品还很远。公司2017年创立, 2018年做了第一个存算一体芯片流片,2020年发布第一个产品,2021年第一代产品进行量产,第二代产品也发布即将量产,现在已经完成大部分测试。

存算一体的内存墙挑战。内存墙就是数据在计算、存储之间需要不停地搬运,需要花的计算功耗,是从内存把数据搬到芯片上消耗的功耗的600多倍,也就是说,真正计算的功耗很低,但是数据搬运的功耗是很高的。这些瓶颈一旦解决,芯片运算效率和速度都有数量级的提升。

为了解决这个问题,整个业界2010年开始就在尝试各种方案。

一类是解决存的问题,一类是解决算的问题。

很多人困惑3D Xpoint是不是存算一体?它可以叫做以存储为中心计算,它还是一个存储器产品,可以在存储和内存的角度去结合两者的优势,速度会比固态硬盘的SSD的FLASH快,密度会比内存的DRAM大,所以它是基于中间的存储器。整体来说,它一般叫内容性存储器,它还是存的问题,是解决存储、解决冯诺伊曼架构当中提高存储运算效率的方式。

另外一种是近存储计算,比如CPU要做一个计算,去比较两个很大的数,在SSD里面,要把数据拿到CPU上,CPU要等1万个时钟周期才能把数据拿过来,而中间的一个计算只需要消耗一个时钟,其实这个时间就白白浪费,整个芯片的效率和计算没法做起来。所以近存储的计算方式,就是说要比较这两千万个数和另外两千万个数谁大,与其把这个数据都拿到CPU中算,不如CPU把指令发到存储的SSD里,SSD有了简单的比较之后,把结果发回来就可以,不需要把几千万个数一个个搬过去,每搬过去一个,GPU都要空白一万个核。所以近存储计算也是解决存储方面的事情。

存算一体中的算也有两种方案。

一种是近内存计算。内存和CPU之间的数据搬运很慢,带宽不够大,功耗很高,把两者距离拉近能不能解决这样的问题?所以内存和CPU之间就可以用先进封装的方式,把中间的带宽提高100倍。这种方式在显卡以及未来的三星以及国内内存厂都在提出这种的解决方案。

存算一体是另外一种。此处的存算一体和很多人口中的存算一体不一样,它或者叫存内计算,实际上是用存储器完成预算,直接用存储单元完成运算,涉及到模拟预算。数字运算必须要逻辑模块,必须要在冯诺伊曼架构下进行,但存储运算可以采用模拟的方式去完成运算,所大家都是在用模拟的运算去提高运算效率,去突破冯诺伊曼架构中的内存墙的瓶颈。

WTM2101是公司第二代产品,知存科技用它做端侧运算,相当于芯片在现有冯诺伊曼架构中的功耗或者说相同成本的情况下,拓展更多的功能,算力也可以提高很多,比如语音识别、语音增强、声纹识别、心电以及简单的物体检测。

上面的芯片是五角硬币芯片的大小对比,是一个WCSP的封装,这个芯片非常小,可以放在很多端侧设备当中。

右边是采用WTM2101芯片做典型的应用场景。其实在跟市场场景对比来看,整体会有10倍到30倍的效率提升,算力可以有一定程度的增加,同时功耗有一定程度的降低。芯片的最大算力可以达到50Gops,但是同类型市场芯片一般算力就是在1Gops左右。

WTM2101芯片的架构,左边是存算一体的NPU,NPU里面有1.8MB权重单元,这是一个单核的计算,中间没有做并行,所以算力可以存储1.8MB神经网络参数。这个存算一体的CPU可以做运算,因为它是FLASH介质,片上的代码和系统也用这个存算一体去实现。所以,它可以做运算又可以存参数,还可以解决真正的代码存储,同时芯片也带有Risc-V的CPU,支持CMD的指令,同时支持三个比较大的算法在芯片上运行起来。目前支持多个传感器的输入。当然,最主要的优势还是存算一体的NPU部分,相对来说它在AI计算当中可以把端侧算力提高20-50倍左右。

芯片真正怎么用?有个MITIN Mapper工具,一个简单的工具或者编译器。存算一体的编译器比起冯诺伊曼架构的编译器,区别是很大的,因为冯诺伊曼的CPU由指令集构成,一般一个乘法运算可能需要四五个指令实现,像一个大的深度学习网络可能需要几千万个指令去实现,挑战难度很大。存算一体的编译很大程度上是粗粒度的编译,因为是用存储器完成矩阵运算,所以真正做的编译过程,就是把神经网络的运算转化成矩阵,把矩阵映射到存储器上。比如一个神经网络可以转化成五个比较大的矩阵乘法运算,把五个矩阵优化,占最小的面积,放到大的存储器阵列上面,只需要5次操作就可以完成运算。比如说第一次选择L1,这是一个大矩阵,可以直接用一次周期完成一层网络的运算,第二次选择第二层,第三次选择第三层。现在存算一体芯片里面同时可以支持最大896×1024的矩阵,小的矩阵也可以比它小,可以做配置,所以大小矩阵都可以通过配置的形式存在存储器。真正去运算的时候,就是依次调用第一、第二、第三、第四、第五层,做五次存储器读取,五层网络就完成了。目前在也映射30多层网络,就是做30多次或者到60多次存储器读写。当然,有一些网络现在做到一百多次的矩阵。

举一个例子,在做语音识别、唤醒、声音检测的时候,经过芯片有一个特征提取,之后传到存算一体里面,网络一般会映射两三个算法,比如说简单的声音检测和语音识别,语音识别词最多支持300个词做识别,功耗一般都是在毫安级别,去做几百个词的识别。完成深度学习运算之后,再把运算的结果放出来。而几百个词的识别,一般在1毫安、2毫安功耗下,在传统芯片只能完成10个左右的词的识别,所以没法做到这么多的词的识别。所以存算一体在低功耗情况下,可以完成很大算力的运算。

另外,存算一体在完成深度学习运算时候的延迟很低。比如说做一个同样大小的深度学习网络,假如涉及到几百万个参数,它光读存储器就要读5万多次才能把数据读取出来,时间很长。换算到存算一体,可能读几十次存储器就把运算完成了,这样延迟就可以做得很低。有了低延迟,就可以完成很多很复杂的深度学习运算,并且功耗很低。目前用的是FLASH,运算完了之后就可以断电了,数据不会丢失。所以,可以用它以完成降噪类的计算。

存算一体的应用场景可以很广,针对不同场景有这样的预测。因为存算一体跟传统的计算特点区别是它的算力正比芯片的存储空间,也就是说芯片中的存储单元数量越多,它的算力就越大。美国一家MEcike的公司可以做到单芯片110多兆的存储空间,单个芯片可以达到35TOPS的算力,这个还是仅仅在40纳米工艺下完成的,想要达到单芯片35TOPS算力,一般都需要在12纳米的芯片。

所以存算一体不同应用场景需要的算力,包括算法容量大小,其实都在进行很多的改变。比如在移动终端,需要算力至少达到30TOPS以上,在AR/VR眼镜上,这是挑战最大的场景,因为它电池很小,散热很小,但是它需要的存储容量又很大,一般像本地的手势识别、自然语言理解都要在本地理解,所以一般需要的存储空间都需要在100TOPS左右,像自动驾驶、服务器需要的存储空间就更大,需要上GB的存储空间。

对于存储器,这是很容易实现的,因为大家手里的U盘都有几百个G的存储。如果未来能够把U盘这么大小里面的几百个G都转化成运算,它就可以达到上千TOPS的算力,超越现在所有的计算芯片能提供的最大算力。这也是一个发展的过程。

存算一体、感存算一体未来还有5-10年左右的发展,运算效率还会比现在再提高10-20倍,应用场景也会越来越广。随着越来越多的人加入,越来越多的客户试用存算一体、感存算一体的技术,更多的场景就会把它用起来。

存算一体第一代量产的是40纳米以上,目前做了小批量,在22、28纳米上都有技术规划,包括未来在Trplite和RRAM都有一些技术的验证。

一个很强大的正向的生态,对存算一体胪其实是非常重要的。因为存算一体的需求就是颠覆现有冯诺伊曼架构芯片,而现有冯诺伊曼架构的芯片已经被大家用了七八十年的时间了。一个新的架构去颠覆传统,不仅说要把算力提升一百倍、一千倍,同时还需要整个生态区用起来,包括客户场景使用,去驱动这个芯片越做越好,在这个芯片基础上开发更多的系统、更多的应用、更多的算法,挑战还是很大的。不是一个公司、几个公司做的事情。

未来50%的场景甚至50%以上的场景都可以用到存算一体,所以它是非常大的市场。真正把这件事情做完,可能需要到400家公司,在未来的市场才够大家分,因为未来可能有几千亿美元的最大的市场。所以目前每年可都有更多的指数级的玩家,包括客户、上下游以及公司加入其中。预计未来5-10年存算一体包括感存算一体就可以分布到50%以上的AI以及大家使用的场景当中。

当天下午,来自后摩智能、 犀灵视觉、每刻深思和知存科技公司的四位嘉宾分别介绍了存算一体及相关技术,浙江大学的四位教授也应邀参与对话。

【以上内容根据演讲速记整理,未经本人审定】