近期,Blocks&Files与三星副总裁DRAM内存规划&支持组负责人Young-Soo Sohn就DRAM、高带宽内存 (HBM)的发展进行了如下问答。

提问:美光对支持未来内存节点的事曾有过报道,三星可以支持哪些内存节点?1Z, 1 α, 1 β还是1 γ?

回答:三星近期推出了基于极紫光刻机技术的14nm DRAM。通过把光刻机的层数提升到5层,能生产出现今尺寸最小,速度前所未有的DRAM节点,计划今年下半年量产基于14nm的DDR5。

另外,我们还在开发新一代工艺节点适应行业内对密度、性能和功耗等要求严苛的应用。

*三星是业内首家在 DRAM 生产中采用 EUV 的公司。 EUV 技术减少了多重图案化中的重复步骤并提高了图案化精度,从而提高了性能并缩短了开发时间。

提问:三星对于DDR5的规划是什么?

回答:已向客户提供样品,并且计划今年下半年量产。

三星正在与行业利益相关者密切合作,在丰富的高性能应用中部署DDR5产品。目前我们正在把DDR5产品系列样品提供给客户,并且不久之后证实他们的尖端产品加速AI/机器学习,超算,分析,网络等数据密集型工作负载。

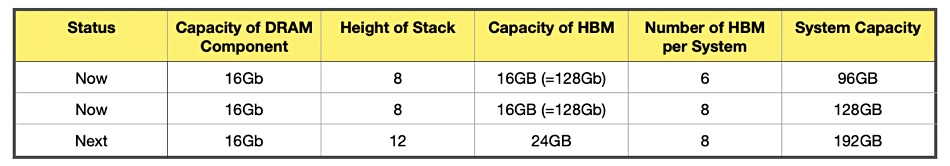

提问:HBM相比DRAM在容量方面的优势

回答:因迭代而异。当前HBM2E标准(第二代 HBM2 扩展版)最高可支持8个堆栈,HBM2E SiP将能够提供128GB的容量。但实际上,目前可用的HBM2E最高容量为16GB。HBM3标准(目前开发中)有望扩展堆叠能力——结合不断增加的设备密度,产生最高的容量。

提问:HBM 相比DRAM在带宽上的优势

回答:HBM 在总线带宽和处理速度上优势最为明显。从第一代以来,HBM标准支持1024比特位总线带宽,GDDR仅支持32位,标准HBM2E信号速率为3.6 Gb (Gb/sec/pin),每个堆栈的带宽最高可达每秒460 GB。在HBM3开发阶段,期望实现高达6.4Gb/sec 的快速处理速度——远远超出许多预期。

与容量情况不同,三星的 HBM2E Flashbolt 设备实际带宽已经超出了标准。相比之下,GDDR第六代DRAM标准指定数据速率为16Gb/秒。对于一个有4096比特位内存接口的处理器,如 GPU和FPGA,八个 Flashbolt 堆栈组合可以提供128GB的内存和3.68TB/秒的峰值带宽——远远超过传统的DRAM。

提问:HBM会支持哪些CPU?至强?AMD?ARM?RISC-V?

回答:三星正在与各类CPU开发人员合作。对于ARM,富士通正在供应,至强/RISC-V目前正在开发中。

最后

三星在DDR5和DDR6内存方面非常活跃,还大力开发其HBM和HBM-PIM 堆叠存储技术产品,并且正在考虑支持X86、Arm 和RISC-V处理器。HBM-Arm和HBM-RISC-V将与至强-HBM系统形成有趣的竞争关系,尤其在具有低延迟、数据密集型处理需求的边缘环境里。