2022中国数据与存储峰会期间,CXL大内存论坛在线上召开,澜起科技技术市场经理邱铮在论坛上发表了题为《CXL内存扩展解决方案》的主题演讲,内容介绍了CXL互联协议在解决内存发展瓶颈方面的价值,并以澜起科技的MXC为例,介绍了具体的实现方案。

以下内容根据演讲速记整理而来:

关于澜起科技的简要介绍

澜起科技是一家国际领先的数据处理及互连芯片设计公司,主要致力于为云计算、人工智能领域提供高性能、低功耗的芯片解决方案。

澜起科技在服务器市场深耕多年,旗下有津逮系列的CPU®,有安全内存模组,可提供高性能的安全服务器平台。在互连芯片方面,澜起科技在服务器内存接口芯片市场上已经处于世界领先地位,如今正积极拓展CXL内存这一新兴领域。

内存系统的发展趋势

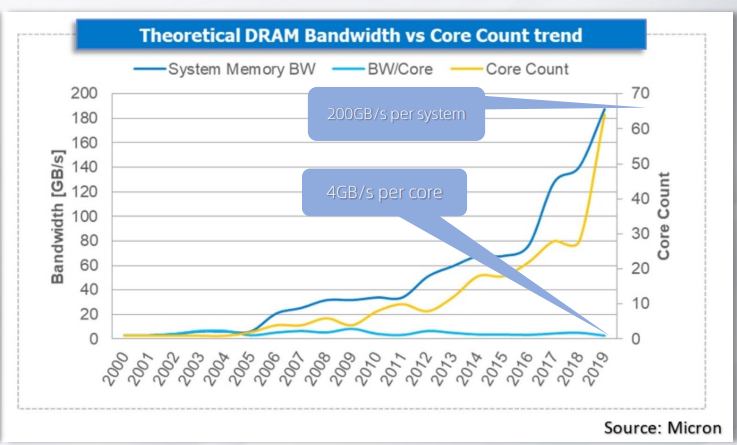

随着云计算、人工智能、高性能计算等技术的发展,处理器的算力不断地在提高,处理器的核心数也越来越多,这也推动了对内存大容量、高带宽的需求。

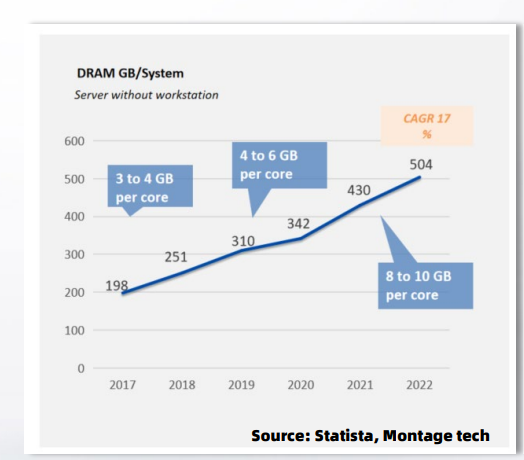

从下图可见,过去几年来,平均分配到每个计算核心的内存容量在不断增加,从早期的3、4GB每个核心,到4-6GB每个核心。2021年,每个计算核心上面平均要分配8—10GB的内存容量。

从带宽来看,虽然整机的内存总带宽是在不断提升,但是相对于核心数来说,每个核心上面的内存带宽提升并不明显。

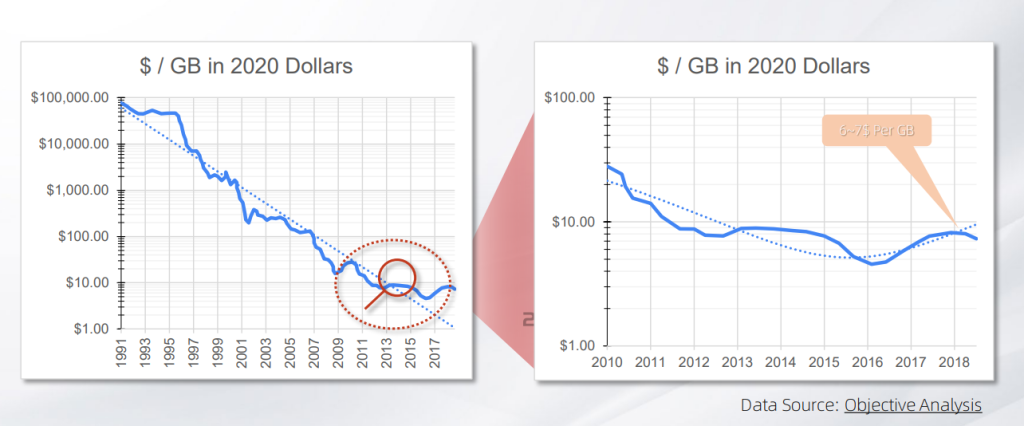

从内存成本发展的趋势来看,过去十几二十年来,随着DDR内存的发展,单位内存的成本在不断下降。但近几年来,下降的趋势变得更平缓了。

很重要的原因在于,由于内存的基本单元之一是电容,而电容的尺寸在目前情况下很难再进一步缩小,这制约了内存制程的进一步提升,随着内存容量不断提升,内存条的成本就会上升。

内存容量和带宽持续发展面临的巨大阻碍

如今,一方面需要更大容量的内存,一方面又需要高带宽的内存访问能力,如何增加内存的带宽和容量呢?

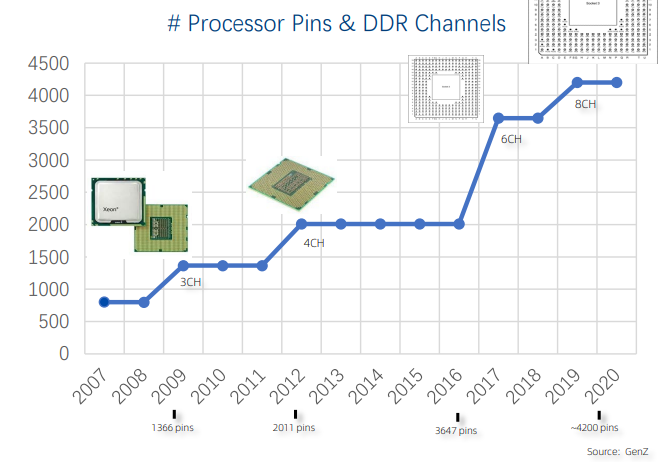

以往的做法中,就是在处理器当中增加内存通道,从上图可见,处理器支持的内存的通道数,从早期的3通道、4通道,发展到了现在的6个内存通道、8个内存通道,将来的处理器还会支持12个内存通道。

然而,处理器支持的内存通道不可能无限地增加下去。

因为,每增加一个DDR内存通道,都要增加很多信号,随着通道数的增加,处理器要处理的信号数量会越来越多,这对于处理器的封装设计,以及主板的PCB设计来说,都是很大的挑战。

另外,随着内存控制器越来越多,也会对处理器的功耗和散热设计带来很多的问题。

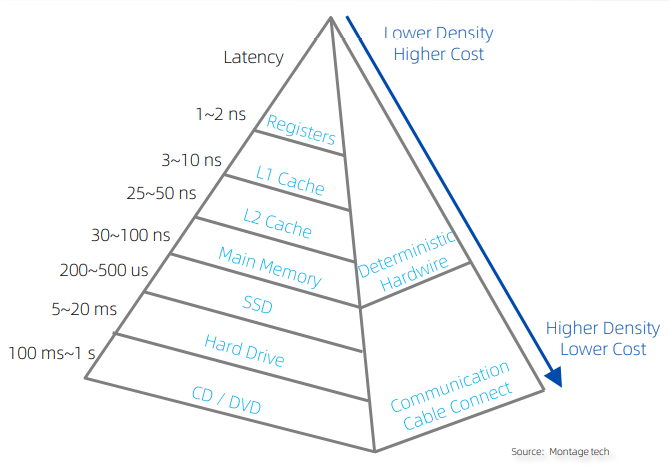

从经济性的角度来看,现有的DDR内存延时低,但是成本较高,市场上出现了一些新的存储介质,虽然延迟比较大,性能比较差,但是成本很低。如果系统能够支持不同的存储层级,意味着成本上面可进行一些优化。

但是,目前处理器主流的DDR接口无法兼容多种存储介质,虽然处理器可以通过PCIe接口来支持其他的存储介质,但无法在系统的角度保持不同存储介质间的缓存一致性,数据传输的效率无法进一步提升。

CXL为内存技术进化提供了新的维度

CXL协议的出现,为解决内存系统存在的诸多问题提供了一个很好的解决方案。

CXL是一个开放的工业标准,由英特尔首先提出,业界许多领先的企业,包括处理器厂商,内存厂商,芯片设计厂商,以及OEM、CSP的厂商,都加入到了这个联盟当中。

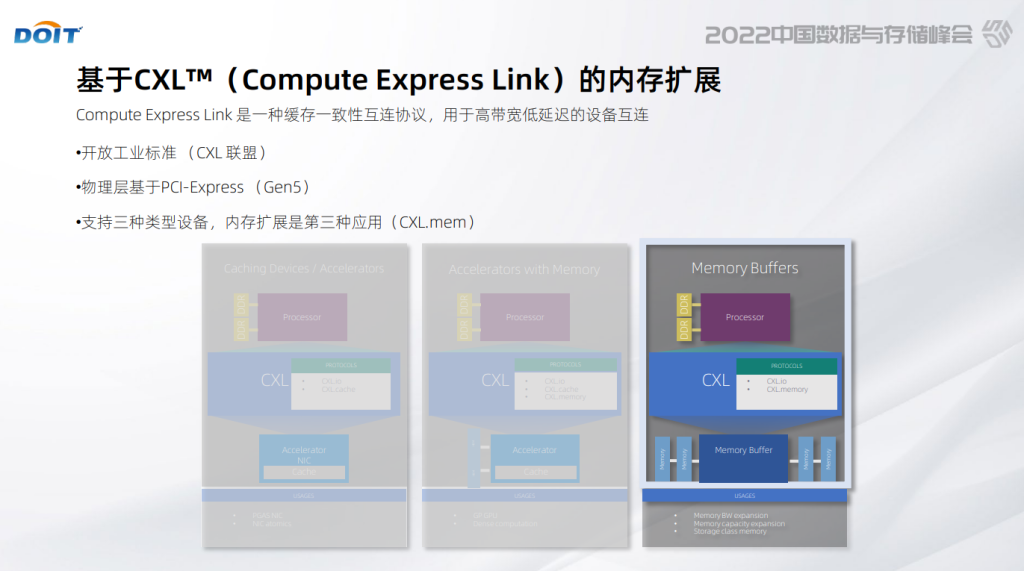

CXL协议在物理侧上沿用了PCIe Gen5的规范,这也为高带宽提供了很好的基础。在物理层之上,它定义了三种不同的协议,根据支持的协议数量的不同,可以把CXL设备大致分成三个类型。

今天我们主要看第三种设备类型,也就是CXL的内存扩展。

设备三的类型,主要是支持CXL.mem协议,主机的处理器通过这个协议,把这个内存读写的请求,发送到CXL的控制器,CXL控制器再把这些请求转给后面的内存控制器,并完成相应的指令。

通过CXL串行接口,处理器可以利用相对较少的信号数量来扩充内存的带宽和容量。同时,CXL控制器来解耦了处理器对存储介质的依赖,使得不同的存储介质都可以通过各自的CXL控制器连到同一个处理器上。

于是,从系统的视角来看,这就形成了可统一管理的、具有不同特性的存储空间。

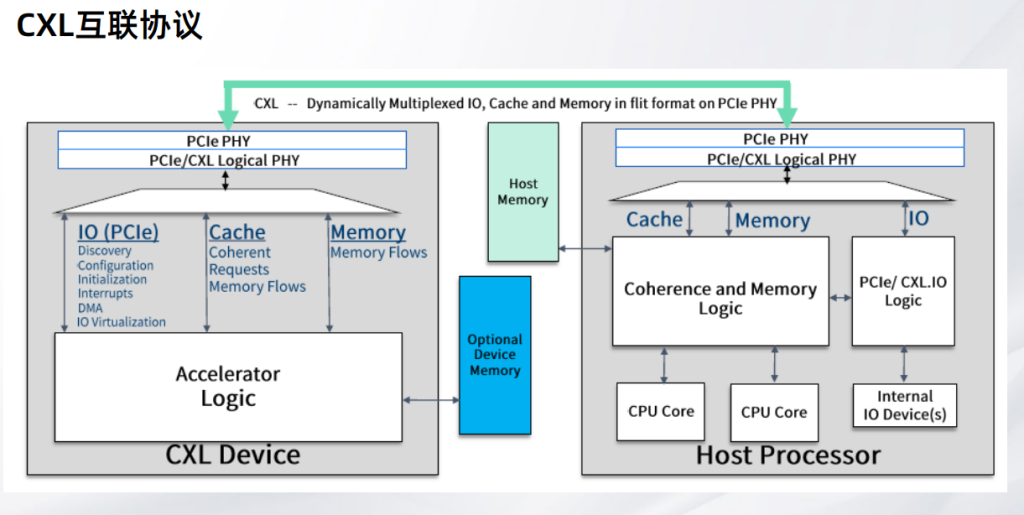

从上图可以看到CXL与主机的连接方式,以及它在系统的体系当中的位置。

左侧是一个CXL设备,右侧是一个支持CXL协议的处理器,两者主要通过三种协议连接到一起的,分别是:CXL.io,CXL.mem和CXL.cache。

CXL.io协议跟PCIe的协议基本上保持一致,主要用于设备的发现、配置、初始化,还有一些中断等服务,CXL.io的数据和PCIe一样,都是走到处理器的IO部分。

CXL.cache和CXL.mem是CXL新定义的协议:CXL.mem协议主要用于处理器访问设备内存,CXL.cache协议主要是用于设备来访问系统的内存。

这两种协议的数据,跟CXL.io不同,它是统一纳入到处理器的内存一致性管理单元。所以,它的数据延时相比于传统的PCIe或者说CXL.io来说就能够大大地缩小。

从逻辑上来看的话,设备的内存控制器,就等价于处理器的内存控制器。设备上的这些异构处理核心,包括GP-GPU和一些加速器单元都等价于主机处理器的计算核心,等价于CPU的核心。

从主机处理器的角度来看,内存发过来请求,都是从内存一致性管理单元发出来的。根据内存请求不同的地址范围,这些请求,要么发送到处理器自己的内存控制器上面,要么发送到CXL设备上面的内存控制器。

同理,设备商的计算核心的内存访问请求,也跟跟主机处理器一样,也需要发送到内存一致性的管理单元。由内存一致性管理单元来处理各个缓存的一致性的问题。最后才将相应的数据,发送到设备上的计算核心。

如此一来,内存、设备的内存,在系统中是统一分配和管理的,它由主机和这些设备共享,还能保持缓存的一致性,这就使得数据的访问效率大大地提高。

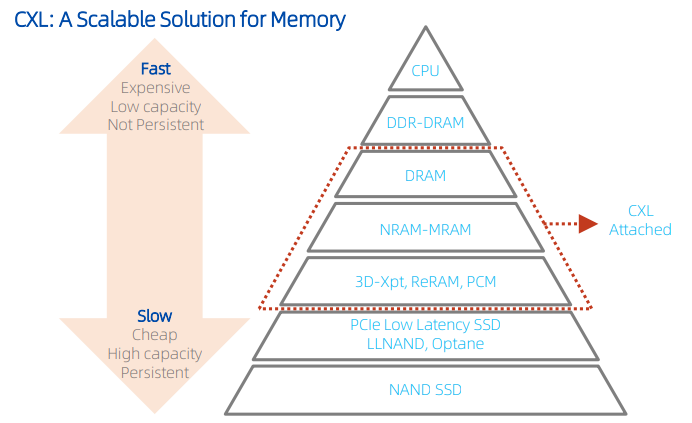

CXL内存模组是使用CXL作为内存互连技术的内存模组,它摆脱了传统DDR模组的限制。

如上图所示,它可以把不同的成本,不同性能的存储介质,通过CXL的接口连接到系统当中。

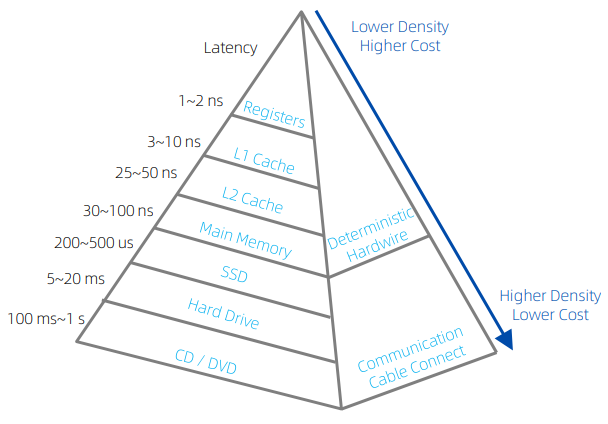

上图是传统的存储层级图,传统的DDR内存延迟是在100纳秒左右,传统的SSD设备的延迟在100微秒的级别,两者中间存在很大的Gap。

CXL可以连接不同的存储介质,填补中间的空档,使得整个内存系统在性能上和成本上都得到了大幅优化。

澜起科技在CXL产品上的进展

澜起科技作为CXL联盟的成员之一,也很早就启动了CXL内存扩展项目。

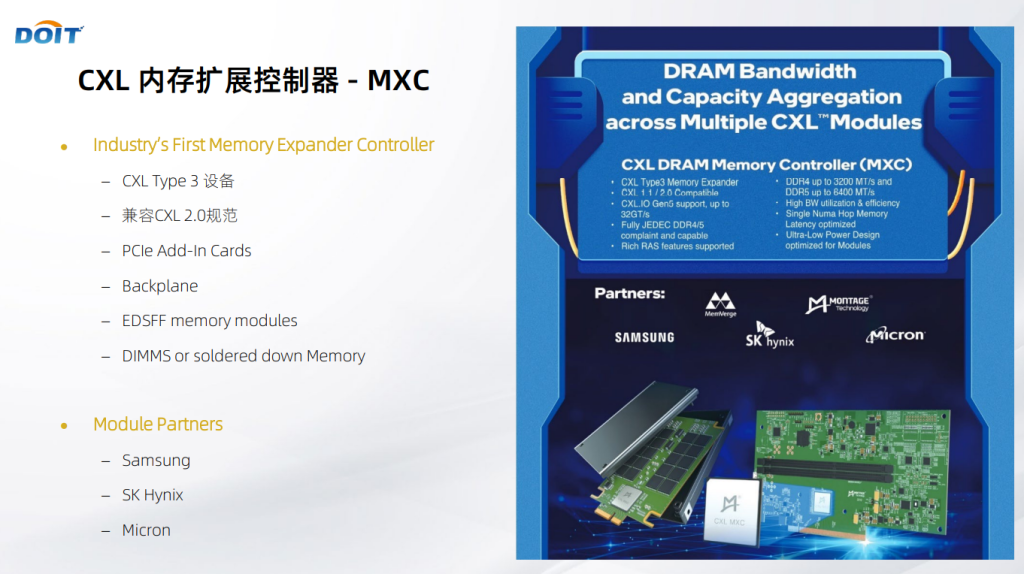

2022年第二季度,澜起科技研发生产出了业界第一款的CXL内存扩展控制器,叫Memory Expander Controller,简称MXC,它属于CXL第三类的设备,也就是CXL.mem设备。

MXC兼容CXL 1.1和2.0的规范,支持标准的DDR4和DDR5接口,可以广泛地应用在不同的模组类型上。比如传统的PCIe卡的形式,或者是新型的EDSFF的形态,或者服务器的背板。

MXC支持标准的DIMMS内存条,也可以支持内存Onboard的设计。澜起科技在很早之前就跟业界主流的DRAM厂商、平台厂商,像MemVerge这样的软件方案厂商展开合作,来共同推动CXL生态的发展。

MXC芯片能够为处理器提供高带宽、低延时的内存访问,实现高效的内存资源共享,降低系统软件栈的复杂度,降低数据中心总体内存的成本。

CXL控制器方面,MXC芯片支持CXL.mem和CXL.io协议,物理层上是一个X8 PCIe5的接口,最高速度能够支持32GT/s。MXC芯片支持丰富的RAS特性。

DDR控制器方面,MXC芯片兼容JEDEC标准的DDR4/5的规范,可以支持UDIMM、RDIMM和OnBoard的设计。支持的速率最高DDR4-3200MT/s,DDR5-4800MT/s,还支持一些低功耗的模式。

MXC芯片是内存扩展和池化的关键器件。

在一个服务器的节点当中,MXC芯片可以以不同的模组形态,进行内存的带宽和容量扩展,满足一些高内存带宽的业务需求。也可以在新平台中,继续使用DDR4的内存条,来降低内存的成本。

随着将来CXL 2.0平台的推出以及Switch交换机的推出,多个CXL的模组还可以组成一个内存池,通过Switch交换机连接到多个服务器节点,灵活地满足各台服务器对内存的需求。

内存池化应用的价值

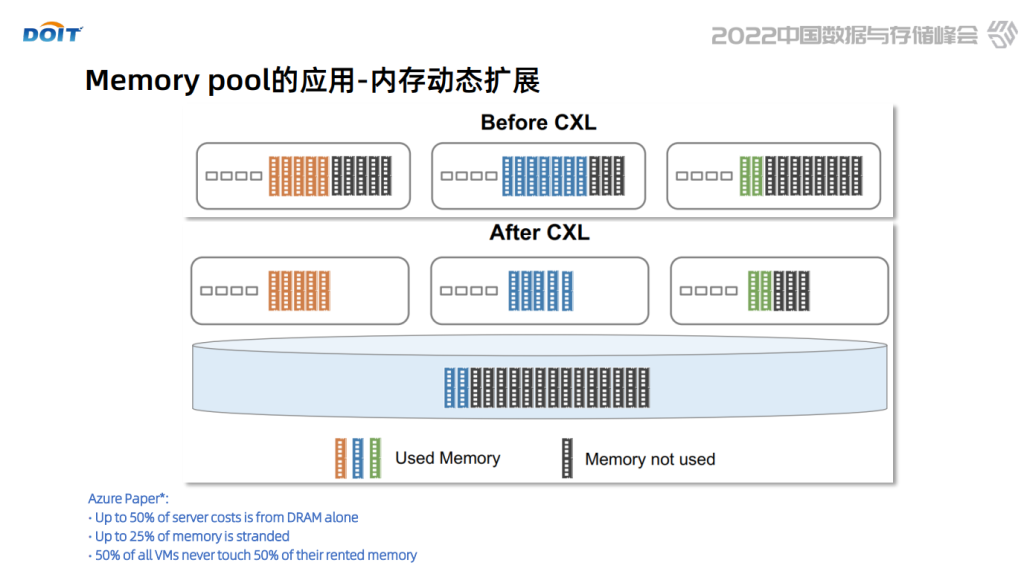

在CXL技术出现之前,内存和处理器是紧耦合的,内存都部署在服务器节点内。

有调查发现,内存成本是占整个服务器成本的比例很高,但是在实际使用中,内存的使用效率并不高,有的内存空间根本没有被访问,有的内存空间则存放了一些比较冷的数据,它访问的频率其实很低。

这部分的内存没能很好地发挥它的价值,如果用CXL来做池化,这意味着单节点服务器可以部署较少的内存,大部分的内存可以从服务器当中解耦出来,通过CXL技术,形成一个内存池,连接到多个服务器上。

在使用中,通过Switch将内存动态地分配到有需要的服务器上,从而可以大大提高内存的使用效率,使得数据中心用较低的内存成本,能够满足实际业务的需求。

以上,就是此次分享的主要内容,澜起科技关注到CXL会推动数据中心的内存架构的变革,也将继续跟我们的合作伙伴一起,为CXL技术的发展做出贡献。