3月31日,铠侠与西部数据联合发了最新的218层3D NAND技术——采用1 Tb TLC和QLC,有四个平面,据说是采用了先进的横向缩放和晶圆键合技术,能将比特位密度提高50%以上,适用于以数据为中心的应用,如智能机、物联网设备和数据中心。

两家公司推出的突破性创新之一是CMOS直接键合阵列 (CBA) 技术。 每个CMOS晶圆和单元阵列晶圆都在其优化条件下单独制造,然后粘合在一起提供增强的比特位密度和加速NAND I/O。 NAND I/O速度超过3.2Gb/s,比上一代产品提速60%,加上写入性能和读取延迟提高20%,将为用户提高整体性能和可用性。这一技术促成了第八代BiCS闪存的成功推出。

暗中观察

其实这次的200层+发布应该是在情理之中。大家比较关注的是这次特别提到的晶圆键合技术,因为最早听到是长江存储的Xstacking技术采用了晶圆键合(Wafer bonding)。

先回顾一下前几年的事儿,全球3D NAND市场竞争趋于白热化,谁能早早量产上百层+NAND就能抢占市场先机。本来在层级堆叠上一直领先的是三星,但是当它正奋力产出128层的时候,其他竞争对手突然迎头赶超,然后市场上就有了字符串堆叠( string stack)和单一堆叠(single stack)这两种堆叠方式的取舍争端,三星显然选的是后者在速度上吃亏了。

两种堆叠方式都可行,但各有利弊。单一堆叠(single stack)相当于原生的垂直堆叠1xx+,仅一道工序,有成本优势,但制程复杂度随层数攀升不断加大,蚀刻和沉积最终可能导致裸片良品率下降,比如上述提及的高纵横比,纵横比精度提高会导致沉积和蚀刻步骤中出现许多潜在问题,包括交叠层厚薄不均、蚀刻不彻底(打孔未到达底部)、弯曲、扭曲及线宽变化。还有其间电子垂直通过的迁移率也在随层数增加而更加不可控,这些都是亟待解决的问题。

而字符串堆叠(目前主要指双层堆叠),制程复杂度相对较低,只要你有拥有成熟的48层,64层技术,那么实现248(96)层,264(128)层不是梦,还降低了打孔的蚀刻深度,良品率不会受到影响,但这是两道工序,会增加30%+的成本,容量虽然提升了但很难平衡进程时间和成本的增加。

两种打法,一个快一个稳,再加上长江存储的晶圆键合技术(非堆栈方式),是把一片晶圆上加工负责数据I/O及记忆单元操作的外围电路,另一片晶圆上加工存储单元,最终通过数百万根金属VIA(垂直互联通道)将二者键合接通电路,但成本同样有所增加。“顶层”之战就此打响。

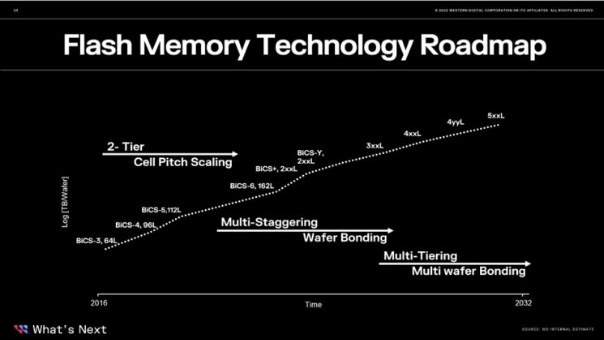

其实之后大概在2022年5月份,西部数据曝出的最新闪存技术路线图上就出现了晶圆键合技术,当时没怎么注意这张图里已经有提到键合技术大意是——200层+闪存是面向高容量和高性能的数据中心工作负载设计,采用了类似字符串堆叠的技术,即多重键合(multi-bonding)和PLC(5bits/cell)技术。

不只是晶圆键合,未来还有多重键合,这次发布的218层还没有加PLC,好奇这里的晶圆键合是什么?跟长存的晶圆键合有什么区别?还是说三家提到的晶圆键合技术是实现未来更高层级必须采用的技术?