新一届国际固态电路会议ISSCC 2010开幕之际,AMD也公布了其首颗Fusion融合处理器"Llano"的更多细节,包括处理器和图形核心资料,以及三种新的电源管理技术–全新的"APU"(加速处理单元)即将到来。

一、Llano APU:32nm四核心加DX11图形核心

Llano的首颗样品已经出炉,并将在今年上半年提供给客户。新处理器采用GlobalFoundries 32nm SOI高K金属栅极(HKMG)工艺制造,相比于传统的多晶硅栅极能明显改善性能功耗比和架构弹性,另外还有11个铜金属层和低K电介质、基于硅锗的拉伸硅、第二代沉浸式光刻技术。

Llano将在2011年提供给OEM客户并正式发布,正好对应Intel的Sandy Bridge,后者也是32nm工艺并整合图形核心,但仅仅是DX10级别。

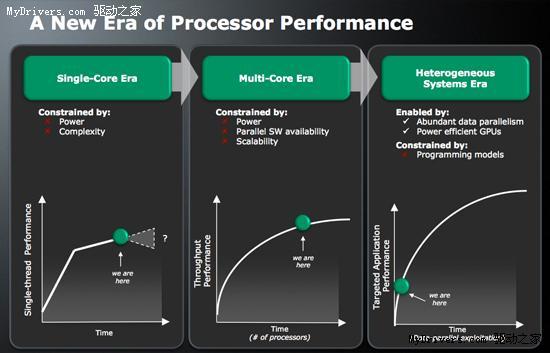

对AMD来说,Fusion融合策略将是从单核心到多核心之后的又一重大转变,处理器也将从单纯的CPU进化到APU,并由此进入混合系统世代,最显著的特点就是大规模数据并行和高能效图形核心,不过难点是软件编程模式必须随之改变。

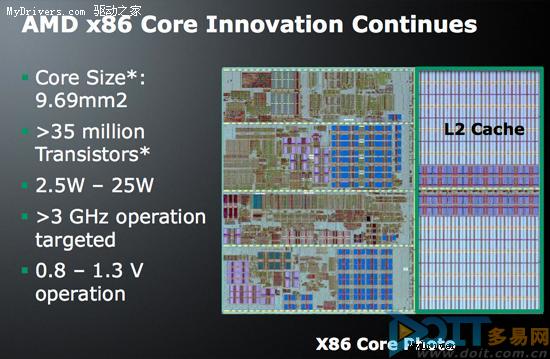

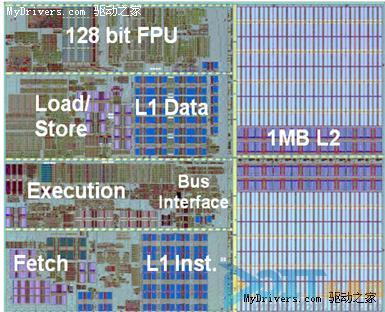

Llano APU由两部分组成,一是四个传统的x86处理器核心,每核心面积仅仅9.69平方毫米,集成3500多万个晶体管,功耗2.5W到25W不等,目标频率超过3GHz,运行电压则在0.8-1.3V范围内,另外每个核心拥有1MB二级缓存,总计4MB。

Llano APU的处理器演变自Phenom II,但砍掉了三级缓存,因此更像是Athlon II,另外在改用新工艺的同时架构也有所优化调整,性能上相信会更进一步。

第二部分是整合的图形核心,衍生自现有的Evergreen Radeon HD 5000系列,因此可以支持DX11,比Intel Sandy Bridge明显胜出一筹。

二、Llano APU的三大电源管理技术

在介绍Intel Nehalem、Westmere两代处理器的时候,我们曾经说过新的功率门限技术(Power Gate),能够几乎完全关闭空闲核心以降低功耗、减少漏电,还能动态提高激活核心的频率。

AMD Llano也会支持这种技术,称之为"Core Power Gating"(核心功率门限)。AMD表示,得益于其SOI工艺,能够做到核心级别的功率门限控制,对晶体管效率和芯片封装均大有好处,还能将漏电率减少到十分之一乃至更低。

Llano还有一个新增的"Digital APM Module"(数字APM模块)。AMD声称,为了达到处理器核心性能功耗比的全面最优化,响应迅速的电源管理机制是非常关键的,而现在普遍使用模拟方式探测核心温度与电流以动态决定运行频率,很容易受外界环境、处理器内核差异的影响,需要很大的容错率,而AMD的数字式新技术能带来更好的精确性和全面的可重复性,从而大大提升性能。

第三种新的电源管理技术直译过来叫作"功率感知时钟网格设计",能将时钟切换功耗降低一半以上。对现代处理器来说,让其整体都保持同步稳定频率并不是很简单的事儿,也会吃掉不小的功耗,能有所改进自然会很重要。

结语:

根据Intel最新内部路线图,Sandy Bridge架构处理器的批量发布已经推迟到2011年上半年,很可能是第一季度。AMD Llano也将在2011年提供给OEM客户,具体发布时间不明但应该就会在明年上半年。如此一来,Intel、AMD将直接展开正面对战,都是32nm 工艺,都是多核心加图形核心,势必会非常精彩。