近期,东京工业大学的Takayuki Ohba 教授及其同事设计了一种3D DRAM堆栈用于处理单元和内存,命名为BBCube 3D,Ohba教授称已将其与两种当前最先进的内存技术——DDR5和HBM2E进行比较。其实验结果为BBCube 3D能够实现带宽为1.6 TB/s,比 DDR5高30 倍,比HBM2E高四倍,比特位访问能耗方面,BBCube则分别是HBM2E的1/20,DDR5的1/5。

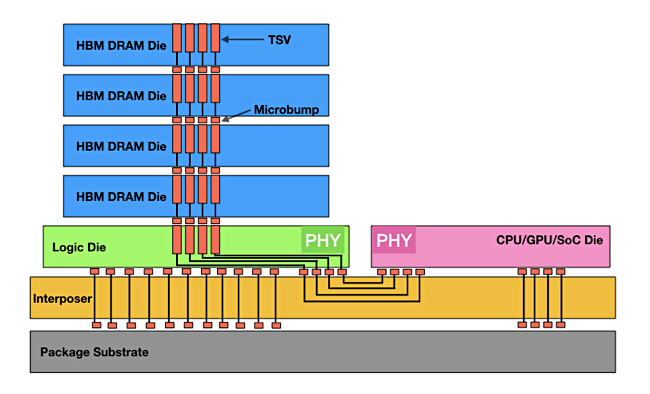

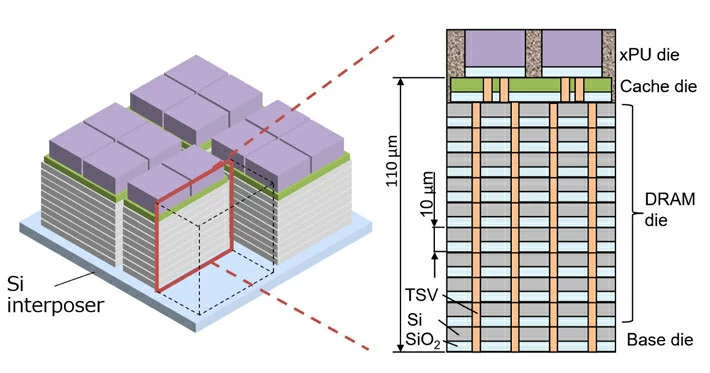

HBM 是一种基于3D堆叠工艺的DRAM内存芯片,缓存和内存组的CP,用TSV(硅通孔技术)实现垂直堆叠,CPU周边像堆乐高一样增加了很多“凹槽”连接多个DRAM芯片。BBCube 3D实现了 PU(处理单元) 和 DRAM 之间的三维连接,处理单元芯片位于多层 DRAM 之上,所有层均通过硅通孔 (TSV) 互连,缩短连接长度,从而获得更好的整体电气性能。

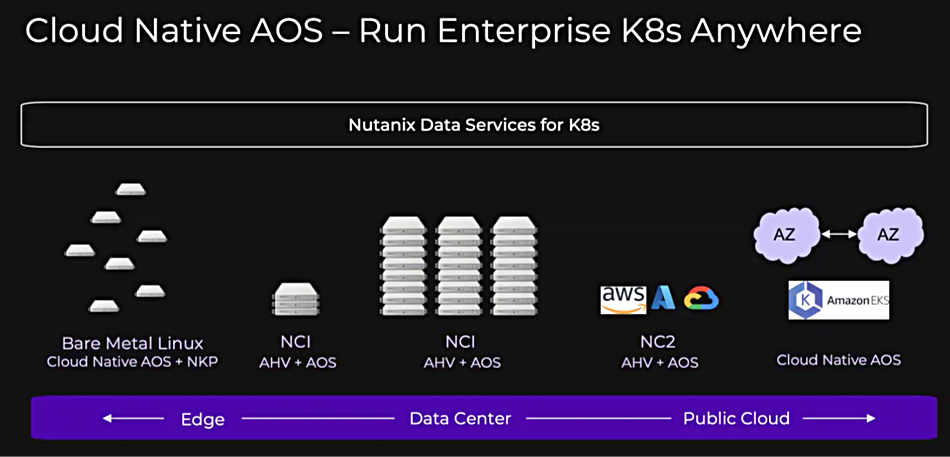

HBM是这样:

图片转自Blocks and Files

BBCube 3D是这样的:

图片转自东京工业大学

也就是说,BBCube3D削薄了每个 DRAM 芯片,去掉了晶圆叠层 (WOW) 设计中的微凸块。与DDR5 或 HBM2E(第二代高带宽内存)设计相比能让内存块以更高的速度和更低的能耗运行,因为前者运行温度更高,并且凸块会增加电阻/电容和延迟。

HBM 微凸块不仅占用空间,并且芯片必须足够坚硬来承受堆叠层粘合在一起带来的压力。 消除之后,每个内存芯片都可以变得更薄,TSV 更短,有助于热冷却。

BBCube 3D 设计里没有中间层,因为处理单元、CPU 或 GPU 是直接绑定到缓存芯片上,而缓存芯片本身绑定到了DRAM堆栈的顶端。据研究团队称,长度较短的 TSV 互连可为 CPU 和 GPU 等高温设备提供更好的散热方式……高密度 TSV 充当热管,因此即便在3D结构中,温度也相对较低。

此外,他们还实施了一项涉及四相屏蔽输入/输出 (IO) 的创新策略,让 BBCube 3D 具有更强的抗噪声能力。还调整了相邻 IO 线的时序,让它们始终彼此异相,也就永远不会同时更改值,减少了串扰噪声并使设备运行更加稳定。

BBCube 3D是大学的一个研究项目。更多该项目的详细信息看这里https://www.mdpi.com/2079-9292/11/2/236,论文发表于2023年6月的IEEE 2023 VLSI技术与电路研讨会上。