随着现代数据中心工作负载的复杂性和多样性不断增加,CPU 与加速器间的紧密协作变得越来越重要。为了应对这一挑战,2019 年,英特尔、Alphabet(谷歌的母公司)、思科、戴尔、Facebook、HPE、华为、微软 和阿里巴巴等联合推出了一种新的高速互连标准 —— Compute Express Link (CXL)。

CXL是一种开放的高速互连标准,它允许高性能加速器,如 GPU、FPGA 或 ASIC芯片与 CPU 共享高速、低延迟的内存访问。通过在设备之间维护一个统一、一致的内存空间,使得CPU和CXL设备可以共享资源,从而提高性能、减少数据移动,还有助于降低软件栈复杂性。

简而言之,CXL的目标是实现计算、内存和存储资源的动态分配,通过在 CPU 和加速器之间提供共享内存的高速通道,使得这些设备可以更有效地一起工作,提高数据中心的性能和效率。

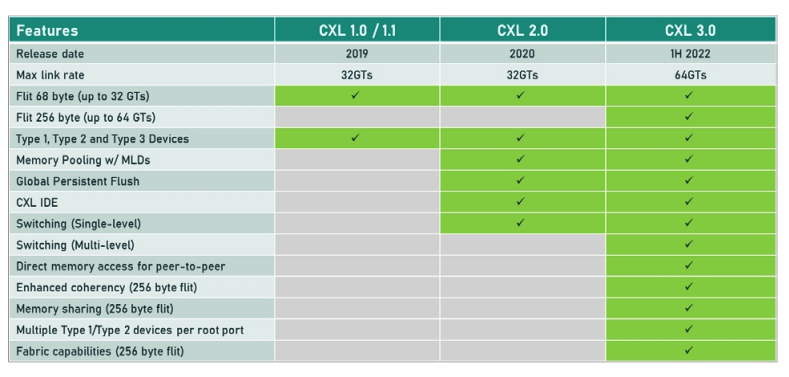

CXL1.0于2019年3月首次亮相,它定义了CXL.io、CXL.cache和CXL.memory三种协议:

其中,CXL.io复用了原来的PCIe协议,在CXL的建立连接、设备发现、配置等过程中发挥重要作用。连接建立后,CXL.cache协议负责做cache一致性的工作。尔CXL.cache和CXL.memory配合起来用来做内存扩展。

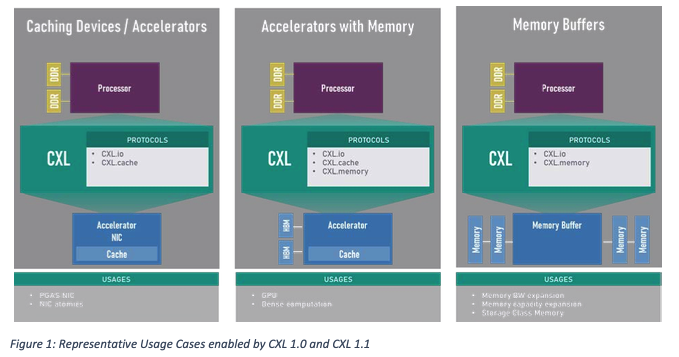

CXL 1.0定义了三种使用场景,对应三大类设备:

第一种主要的应用场景是高性能计算里的网卡(PGAS NIC),它支持一些网卡的原子操作,它主要利用的协议就是CXL.io和CXL.cache。这类设备通常都没有本地内存,比较依赖主机的内存。

第二种主要指的是带有内存的加速器,包括GPU、FPGA、ASIC等加速器,它使用的协议包括用来做链接的CXL.io,做cache一致性的CXL.cache,用来做内存扩展的CXL.memory。

第三种主要用作内存的Buffer,做内存的扩展。它主要利用CXL.io和CXL.memory的协议。在这里,CPU除了可以用本地的DDR内存,还可以通过CXL去访问扩展内存,扩展内存可以是一个大的内存池,可以共享给不同的CPU来用。

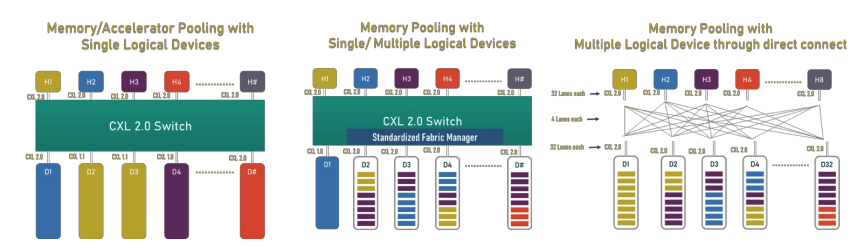

CXL 2.0于2020年11月发布,新增了对于CXL交换机的支持,从而可以用来构建内存池。CXL 2.0支持让主机可以访问透过交换机连接的远端内存资源,它可以在一个机架内通过一套CXL交换机构建成一个网络,构成内存池。CXL 2.0获得了来自计算机业界和用户社区的积极反馈。

2022年,基于PCIe 6.0规范的CXL 3.0发布,与此前基于PCIe 5.0的CXL相比,不仅带宽速率翻倍(延迟没有提高),也新增了很多功能特性,最引人瞩目的当属对于多级交换机的支持。

有了多级交换机的支持,CXL便可以更好地对资源进行解耦和池化,做更多的资源池,比如CPU资源池、内存资源池、网卡资源池和加速器资源池等,交换机之间可以构建各种网络拓扑。

CXL支持最多4096个节点,这意味着它不但在一个机柜内实现计算资源和存储资源的池化和解耦,而且,可以在多个机柜之间建立更大的资源池,如此一来,对于云计算服务商的资源管理效率和成本优化都会带来很大帮助。

从2022年开始到现在,市场上包括三星、美光都推出了基于CXL的内存扩展器产品,而随着英特尔第四代至强可扩展处理器和AMD新一代霄龙处理器的发布,主流的处理器平台都开始支持CXL,CXL的落地便有了硬件基础。(注:目前,AMD支持Type3设备,英特尔支持Type1和Type2设备)

我们也注意到,市场上还有软件解决方案,比如来自MemVerge的大内存软件方案,该软件可以负责管理CXL连接的内存资源,让服务器集群在业务平稳期保有少量的内存,在业务高峰期动态加入额外的内存资源,从而提高内存的使用效率,它可以直接帮助超大规模数据中心节省成本

在现代数据中心,工作负载的需求正在迅速改变。为了处理大数据、人工智能、机器学习等复杂的任务,数据中心需要更强大、更高效的计算能力。CXL 通过提供一种高性能、低延迟的互连技术,可以帮助数据中心更有效地利用计算资源,满足新的需求。