由于内存墙和功耗墙的缘故,现代处理器工业界都走上了多核心设计的道路,通过片内集成多个处理器内核来继续提升多线程运行的性能,而功耗和通过提升频率的方法相比却没有明显的增加。

多核心可以发掘程序的TLP(Thread Level Parallelism,线程级并行度),很多服务器应用具有很不错的TLP,然而还有一些程序线程级并行度并不高,单线程性能仍然是一个重要的指标。

在上个世纪,处理器的单线程性能通过充分发掘ILP(Instruction Level Parallelism,指令级并行度)得到了极大的发展,使用的手段就是超标量、乱序执行等设计,这些设计需要附加复杂的控制线路,因此一些注重功耗的领域–如嵌入式–还可以见到非超标量、顺序执行设计的处理器。并且,ILP的发掘经过数十年的发展似乎已经到了极致,从上个世纪末到现在已经没有太大的进步了。例如,四发射已经成为了通用处理器最多的发射数目,因为更多的发射数量已经不能再明显的发掘ILP,相反,为了充分利用四发射,出现了如 Intel超线程在内的各种CMT技术。

利用多核心系统提升单线程性能

Core Fusion,将多个核心聚合成一个大核心

仍然有一些技术希望继续挖掘TLP和ILP,Core Fusion就是这样的一个技术,通过动态将多个核心聚合成一个大核心,可以灵活地获得多线程性能的提升,也能提升单线程性能,然而基于前面所说的缘故,四发射已经能基本充分地发挥ILP,更多的发射数目、更多的执行单元和更大的L1缓存的提升并不是很明显。Intel Barcelona Research Center提出了一种新的技术:Anaphase,这个技术通过将传统的单个线程在细粒度水平上分解成多个猜测线程(SpMT,Speculative multithreading)并分布到多核心处理器的多个核心上并行执行,最终加速了原单线程的性能。

Anaphase概念图

左:一个传统的单线程,包含了四个大区块和多个小区块

右:Anaphase将其分成两个猜测线程,每个线程具有若干个大区块和小区块

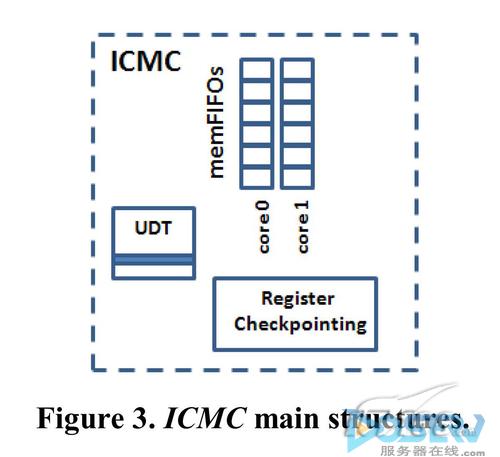

Anaphase是一种软硬结合的方案,软件上,编译器负责将程序的单个线程分解为多个猜测线程并进行标注,硬件上,处理器通过标注将对应的猜测线程分布到多个CPU核心上并行执行,并对他们进行跟踪、同步。Anaphase引入了一个ICMC 组件,将一系列的处理器核心联合起来,这个称为Tile(原意:砖、瓦)的结构就是猜测多线程运行的基本单元。

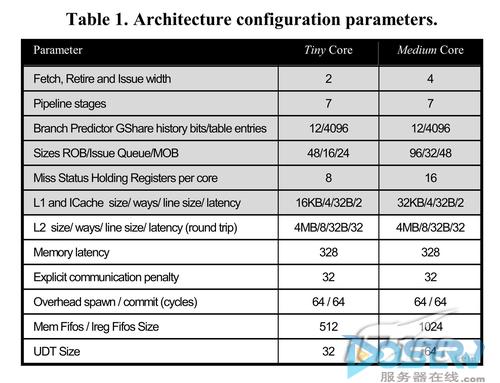

Intel巴塞罗那研究中心使用一个特制的ICC编译器和一个周期精确的x86模拟器进行了 Anaphase的模拟,并和Core Fusion进行了SPEC CPU 2006的对比运算。x86模拟器模拟了下面的两种配置:Tiny Core和Medium Core:

Medium Core就是一个通常的Core 2 Duo核心,而Tiny Core则相当于半个Medium Core

最后Intel给出了四个配置下的数据,基准1则是Tiny/Medium Core下不采用CoreFusion和Anaphase技术的成绩:

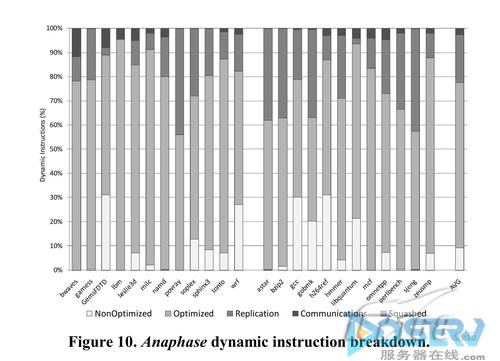

可以看出,Anaphase的效果非常明显 ,在Tiny Core/Medium Core下可以分别达到41%和31%的加速比,Core Fusion技术则是28%和12%,综合上Anaphase比Core Fusion更为有效。

Anaphase动态执行指令分析:测试代码大部分都可以对Anaphase进行优化(Optimized段)

目前Anaphase仍然处于研究阶段,上面的测试是一个基于2核心的Anaphase的 Tile,而Anaphase可以支持更多的猜测线程/运行核心数量,Anaphase技术非常有潜力,唯一令笔者遗憾的就是它还不能脱离编译器而在处理器内完全实现这点了。