Magny-Cours 12核微架构

AMD 24 日于Standford大学举行的 Hot Chip 21 研讨会中,透露了代号为Magny-Cours的12核心处理器的微架构设计,将采用 Multi-Chip Package 技术,把两颗六核心封装在同一颗处理器上,同时将改良内存技术减低内存延迟的出现。今天我们看到了AMD的官方资料信息,接下来就让我们来了解这个由两颗六核心封装而成的12核心处理器吧。

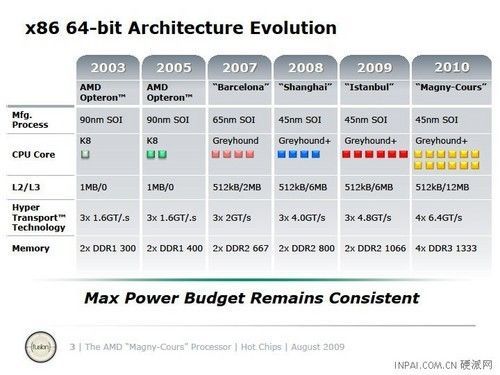

AMD服务器处理器路线图

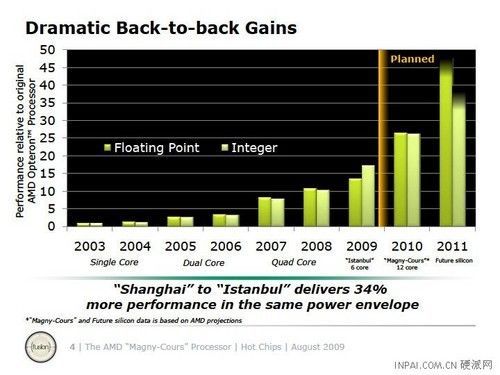

AMD 资深微架构研究员 Pat Conway 指出,即将于 2010 年推出的 12 核心 Opteron 处理器 Magny-Cours 将会采用 45nm 制程,它是由两颗六核心 Istanbul 所组成,并透过Multi-Chip Package 技术封装在同一颗处理器上。

12 核心 Opteron 处理器 Magny-Cours缩微图

Magny-Cours由两颗六核心Istanbul 所组成

HT总线优势带来更灵活12核

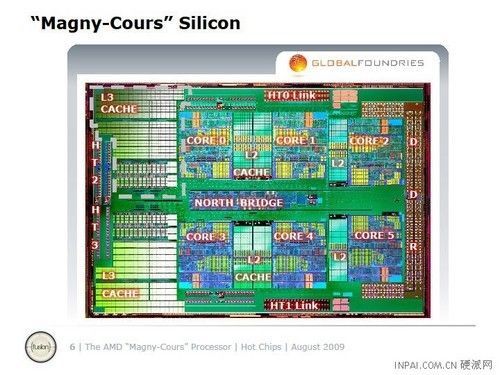

多个核心封装拼接的情况同Intel Core 2 Quad类似,但不同的是Magny-Cours的两颗核心是采用Hyper-Transport 3.0通讯协议直接联系,而不需要像 Intel 采用 FSB 技术,中间通过北桥芯片大幅增加延迟值降低了效率。

两个六核核心通过HT总线进行高速数据交换传输

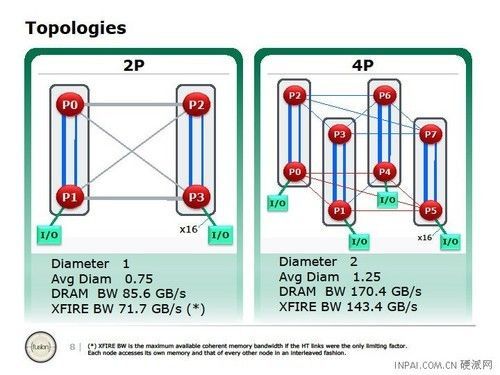

由于制程的进步,让单一Socket 可支持 12 核心,因此现有的 4 Way 系列将可以提供 48 核心的强大运算能力,在同一体积下运算能力将大幅提升一倍。

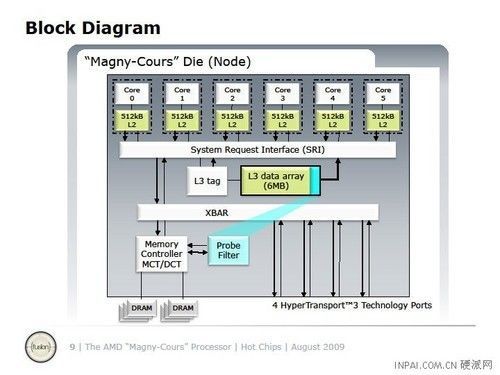

微架构设计方面, Magny-Cours 仍基于现有的 K10 微架构,每一个 Die 拥有六颗核心,每颗核心拥有 512KB L2 Cache,并共享 6MB L3 Cache ,再透过 Hyper-Transport Ports 连接另一颗核心。

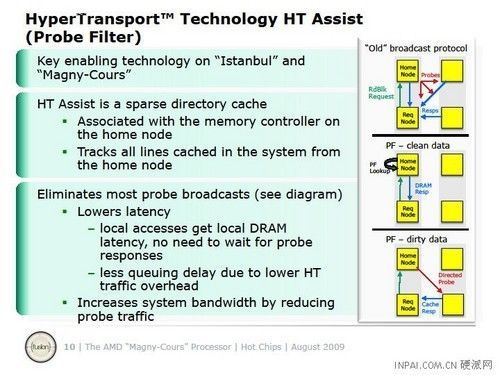

此外,Magny-Cours 支持 HT Assist 技术,处理器的内存寻址数据可存于 L3 Cache 中,约占 1MB 内存空间,储存内存系统的寻址数据,此举将减少内存系统所出现的延迟,由120ns 减少至只有50ns,但 L3 Cache 容量减少将可能减低命中率,不过,Pat Conway 表示HT Assist 对命中率并不明显。

最后,Pat Conway 透露将在 Opteron 处理器中加入类似 Intel Hyper-Threading 的技术,但效果将进一步被强化,相信将会在下一代微架构Bulldozer"推土机"中出现。他并没有透露有关其多线程能力和更多的细节,不过AMD的做法和Intel的HT是不同的,类似Sun的同步多线程功能,1个物理核心扩展到4个线程。

上图是四路Magny-Cours系统,线程已经达到48个。

而官方的测试数据也显示十二核心在整数和浮点性能方面有很大优势。