三周前,甲骨文共同创办人兼首席执行官Larry Ellison首次展示SPARC SuperCluster的同时,还对即将发布的SPARC T系列处理器路线图进行了预览。Sparc SuperCluster是基于现有SPARC T3处理器的Exadata并行数据库计算机。甲骨文硬件开发副总裁Rick Hetherington在接受采访过程中,更加详细地介绍了SPARC T芯片路线图。

在采访中,Hetherington表示,下一代SPARC T4处理器的研发将会在一年之内完成,甲骨文近1000名的工程师参与了这款处理器的研发。Hetherington还补充道,SPARC T4将具有一个新内核,此内核结合了通过线程的吞吐量性能和真正的高速单线程性能。Hetherington进一步表示,甲骨文于2006年和2007年就已开发了此内核,可在2011年进行交付。

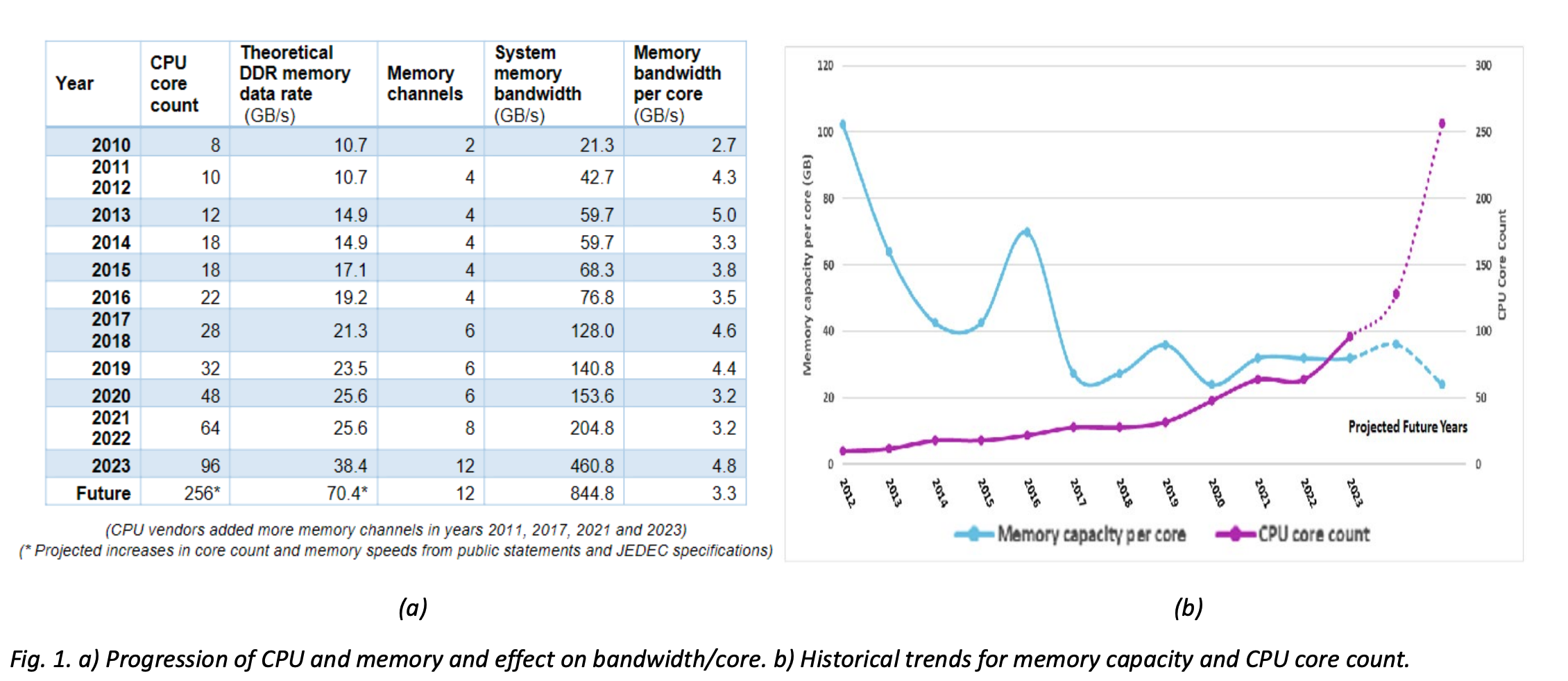

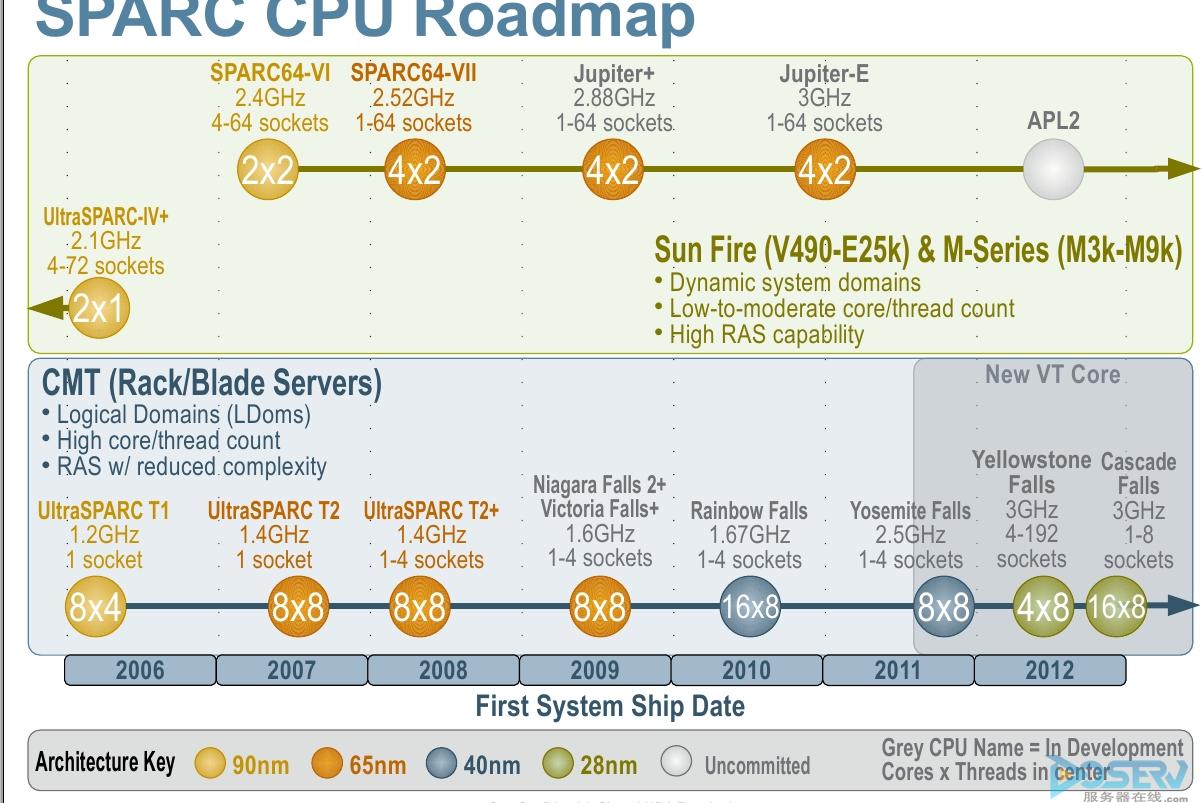

下面我们来看看2009年6月左右的SPARC处理器路线图,这是在取消16核代号为"Rock"的UltraSPARC-RK处理器计划之后,Sun给客户的展示:

甲骨文重温SparcT路线图 T5将采用16核、28nm

SPARC路线图

现有的代号为"Rainbow Falls "的SPARC T3 c芯片,具有16核且每核8个线程,主频为1.65 GHz,采用了Sun的40纳米工艺,并由现在甲骨文的晶片合作伙伴台湾半导体制造公司生产。在Sun的原始路线图上,一款2.5 GHz、40纳米的"Yosemite Falls"将在2011年问世,然后是将在2012年发布的3 GHz 、4核或16核芯片,代号为"Yellowstone Falls"和"Cascade Falls"。Yosemite Falls、Yellowstone Fall和 Cascade Falls都将采用代号为VT的新内核。

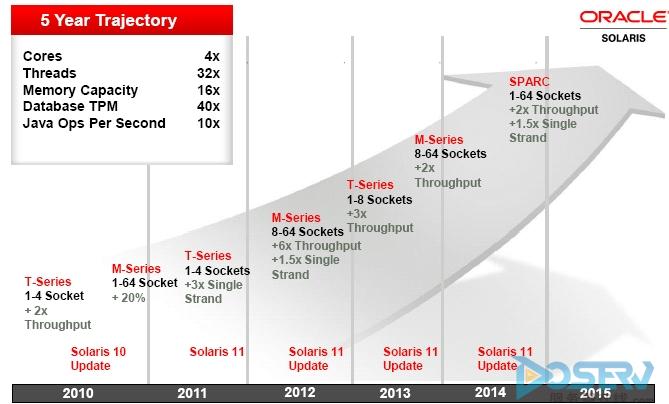

现在来看看甲骨文首席执行官Ellison所阐述的路线图:

甲骨文的SPARC处理器和系统路线图

甲骨文一直希望将"单链"性能(也就是大家常说的主频)提高3倍。笔者期望甲骨文采用Sun以前的方法与IBM和英特尔竞争芯片市场,并认为甲骨文SPARC路线图显示了主频提高3倍将超过现有的SPARC T3芯片,但不会超过2006年的SPARC T1芯片的1 GHz主频。但是如果认为甲骨文指的是后者而不是前者,SPARC T4将仅仅只有3 GHz,而不会达到4.8 GHz 到5 GHz(但笔者在比对现有的SPARC T2+ 和T3一代芯片之基础之上,认为有可能达到4.8 GHz 到5 GHz)。

在笔者看来,甲骨文有可能利用Sun原始的SPARC路线图实现Yosemite Falls处理器,并提升Yellowstone Falls的速度。

Hetherington还在问答采访中表示,SPARC T5将会和现有的SPARC T3一样具有16个内核,并进一步表示T5芯片将实现28纳米工艺。这似乎意味着,Oracle已经结束了Yellowstone Falls,而SPARC T5实际上几乎就是Cascade Falls。

Hetherington解释道,在未来的SPARC T系列芯片中,甲骨文公司将调整芯片的应用程序数据库和中间件堆栈,反之亦然,性能决定了甲骨文应用相关的指令,SPARC T多线程内核中的每个线程将只占用自己所在的线程,而不会共享其他线程的资源,使应用程序可运行得更快。低优先级的应用程序只在可用状态时才获取线程。 Hetherington并没详细说明会产生多少额外系统级性能。

IBM也对Power7处理器核心做了相同的事,其中每个核心加入了4个线程,被称之为智能线程。

另外,笔者还认为甲骨文将可能超频SPARC T4 和T5芯片,使之主频达到5 GHz。当然也可能并非如此,但甲骨文会回避这样一个问题:如果不能实现,是什么原因导致?对于特定的客户群体,尤其是Sun曾主宰的金融服务领域,超频服务器远不及低主频服务器糟糕。

或许超频SPARC T4 和T5系列将有一席之地,且售价高昂,它们需要每年更新一次处理器。因此仔细查看SPARC的部件会发现它们可以4 GHz的速度运行,还需要在芯片中加入先进的冷却系统比如液体块以免高温运行,这就使得甲骨文的产品系列相比IBM和HP的Unix系统更具有竞争力,同时还可赶上英特尔高端至强服务器的前进步伐。

这并不是妄想,Appro International 和Silicon Graphics已经开始出售超频至强服务器。

所以甲骨文销售超频SPARC T服务器也不是没可能的。