7月29日,IBM针对金融业和关键业务领域发布了System zEnterprise 196大型机(前一代是z10),在宣讲了很多架构优势和多样性技术之后,IBM并没有透露更多z系列新四核处理器的规格信息,唯一谈到的技术点就是该大型机的处理器主频为5.2GHZ,且是全球最快的微处理器。

虽然IBM的高管对于公司硬件的运行速度和某些特定性能等信息都比较敏感,不愿多透露详细信息。但近日我们通过国外媒体挖掘出有关z系列大型机中独特的Z处理器的有关细节,与众位读者分享这"神秘"处理器的独特设计。

四核Z196处理器和4.4Ghz的四核Z10处理器有某些相似之处。不过,Z196处理器采用的是 45nm制作工艺(Z10芯片采用的是65nm ),这意味着IBM可以将更多的应用集成到这个芯片上,类似于早先发布的8核Power 7。

据了解,Z196处理器有14亿个晶体管,面积为512.3平方毫米,这使其在晶体管数量和面积上都要大于POWER7芯片。z196芯片采用了IBM的触点陈列封装,被称为C4的金属触点封装取代了以往的针状插脚–其触点数量惊人:8093个电源触电和1134个信号触点。

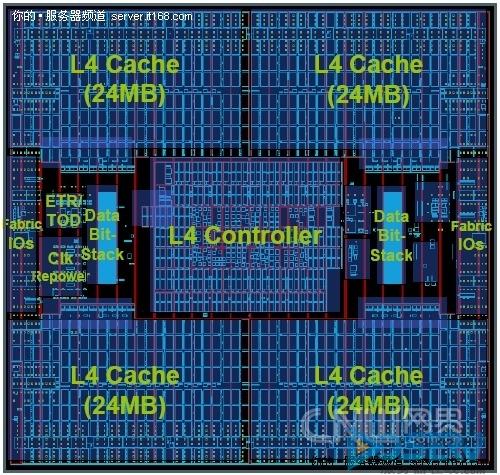

z196芯片和Z10的一样,每个核心都有64KB的L1指令缓存和128KB的L1数据缓存,这一点非常相似。但是z196有100个新指令和超标量通道允许指令重新排序,这样Z196通道就比z10的更有效,而且其编辑代码是不可见的。除此之外,Z196的每个核心都有1.5MB的L2缓存。下面是z196的芯片架构图:

图:IBM z196大型机芯片

z196引擎的超标量通道可以在每个时钟周期内解码3个z/Architecture CISC指令并执行多达5个操作。每个核心有6个执行单元:2个整数单元,1个浮点单元,2个加载/保存单元和1个小数单元。IBM表示,这个浮点单元要比z10芯片中的更好,但是并没有透露它在每个时钟周期内可以做多少flops。z/Architecture CISC中的一些优先级别高的指令被分割成块,这不仅使得通道的使用更高效,还让z196更像RISCy。

与POWER7芯片一样,z196在芯片中采用嵌入式的DRAM(eDRAM)作为L3缓存。这种 eDRAM比经常用作缓存的静态DRAM(SRAM)速度更慢,但是你可以将信息其指定到特定的区域。对很多工作负载来说,芯片可用调用内存的大小比高速度内存更重要。基于这点考虑,z196处理器设计了24 MB的eDRAM L3缓存,每个缓存划分为2个存储体,并由2个片上L3缓存控制器进行管理。

每个z196芯片可以作为一个GX I/O总线控制器–这种方法同样被用于POWER系列芯片中,用于连接主机通道适配器和其他外围设备,每个插槽分配得到一个与受RAID保护的DDR3 主内存相连接的内存控制器。此外,z196芯片还有2个加密和压缩处理器,IBM大型机将采用了这种第三代电路设计。

z196芯片采用两个核心共享其中一个协同处理器方式,且每个核心有16KB的缓存空间。最终达到每个 z196芯片有一个可连接SMP Hub/共享缓存芯片接口。如下图所示,有2个芯片被集成到一个z196多芯片模块(MCM)上,提供了交叉耦合允许MCM上所有6个插槽通过40GB /s相连接。Z196提供的交叉耦合访问方式,在MCM上提供了六个插槽以40GB/s的速度连接到各芯片上。

图:zEnterprise 196 SMP Hub/共享缓存

在IBM大型机中,z196处理引擎相当于中央处理器(CP),而CP的互连芯片称为共享缓存 (SC)。每个SC有6个CP接口相互连接,其中有3个架构接口连接到全加载的z196系统中其他3个MCM。

从上面的架构图来看,SMP Hub的一个优点就是可以加载到带有L4缓存的组件上,这是大多数服务器所没有的功能–几年前IBM曾向至强处理器的EXA芯片组上增加了一些L4缓存。L4缓存之所以重要,其原因在于大型机引擎的主频要远高于主内存速度,但是如果只通过增加一个缓存层来满足Z196的引擎需求是非常昂贵的。不管怎样,这种SMP Hub/共享缓存芯片和CP一样也是采用45nm制程工艺,有15亿个晶体管,面积为478.8平方毫米,封装中有8919个触点。

每个MCM上部署6个CP和2个SC,MCM是一个边长96毫米的正方形,功耗1880瓦。每个处理器板有一个MCM,这使得一个完全连接的系统可以达到96个CP,十几个控制器可以访问多达3TB RAID内存,32个I/O Hub接口最高可实现288 GB/s的I/O带宽。顶架式zEnterprise 196 M80设备中的80个CP可用于运行工作负载,其他可以使用Parallel Sysplex集群来耦合系统、管理I/O和热备份等等。