今年八月初,NVIDIA获得了美国国防部下属国防高级研究规划局(DARPA)的2500万美元专款支持,用于联合Cray、橡树岭国家实验室、六所美国顶尖大学共同研究基于GPU的百亿亿次(Exascale)高性能计算技术,速度千倍于目前最快的超级计算机系统。很快,NVIDIA就披露了他们的相关规划,项目代号"Echelon"。

NVIDIA架构研发主管Steve Keckler解释说,Echelon芯片的基本组成单位仍是流处理器(SP),每八个组成一个流式多处理器阵列(SM),双精度浮点性能大约 160GFlops(每秒十亿次运算);然后128个SM阵列并排,总计就是1024个流处理器,再辅以八个类似CPU的延迟优化核心,共同组成一颗大规模高性能计算芯片。

按照NVIDIA的设计,这样的一颗芯片能够带来20.48TFlops(每秒万亿次运算)的双精度浮点性能,可搭配256GB内存,带宽 1.6TB/s。

相比之下,现在的Fermi(费米)架构在512个处理器、1544MHz频率下只有0.79TFlops的双精度浮点性能,这就意味着 Echelon芯片必须实现25倍的浮点性能提升。再加上相应原型系统预计2018-2010年才能问世,其核心架构应该是下两代Kepler(开普勒)、Maxwell(麦克斯韦)之后的事儿了。

NVIDIA百亿亿次超级计算芯片更深入细节

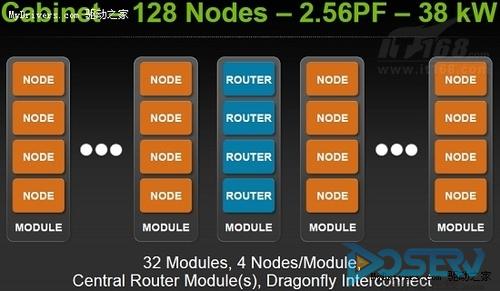

每颗Echelon芯片可以视为一个节点,进而四颗组成一个模块,然后32个模块再加上路由模块就组成一个机柜,合计性能高达 2.56PFlops(每秒千万亿次运算),内存容量32TB、带宽205TB/s。更进一步,这种机柜还可以继续多个并联,浮点性能自然也是继续直线上升。

NVIDIA同时表示,为了降低如此超大规模芯片的功耗,流处理器必须以不到10皮焦的耗电量处理一次双精度浮点操作,相当于费米架构的二十分之一,同时每个流处理器必须在单个时钟周期内完成四次浮点操作。

更进一步地,NVIDIA计划在芯片内集成1024个可配置的256KB SRAM Bank。如此大容量的片上内存能够尽可能地将数据保留在芯片内部,距离处理单元也尽可能的近,从而避免非常耗电的拾取操作。这些SRAM Bank既可以配置为通用内存池,也可以作为专用缓存。

NVIDIA百亿亿次超级计算芯片更深入细节

Echelon现在还只是NVIDIA远景规划图上的一个设想,实现起来还有太多难题要解决,不止有硬件设计上的麻烦,还需要自我感应操作系统、自我感应运行时、位置感应编译器和调试器的软性配合。

有趣的是,美国国防部DARPA也同样找上了Intel,希望其能够从传统CPU的角度出发,同样实现百亿亿次高性能计算。 Intel的计划是利用其正在研发的超多核心(MIC)架构,而且已经有了测试样品,甚至会在今年内推出相应的商用产品,似乎更快一步。

很显然,这是CPU、GPU之间的一场终极对决。